# I/O Connectivity Chiplet Rishi Chugh

6/19/2022

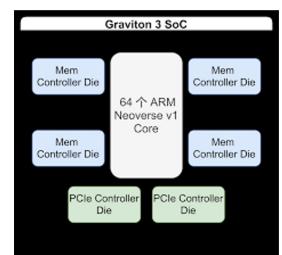

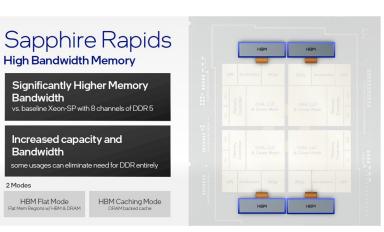

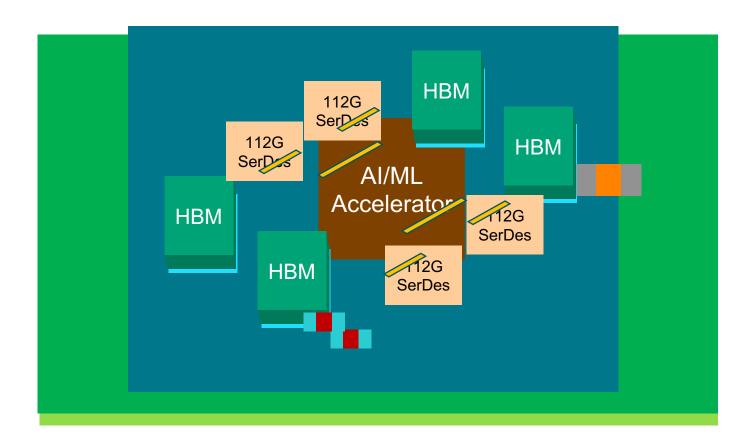

# Chiplet Examples for Heterogenous System Design (KGD)

HBM - Cache Extensions

PIM (Processing In Memory)

Packet Buffering / Look Ups

Data Analytics / Cache Ext

New Design paradigm, from IP reuse to Chiplet reuse

2 Modes

- Primary drivers for chiplet functionality:

- Multi-Core

- GPGPU

- CPU + Workload accelerator

- Scientific computing

Memory / Storage

Host / Client / IO Peripherals

Server SoC (CPU+Chipsets)

WEB servers , Fabric , NIC

NoC (Chip / Interposer)

CONNECTIVITY

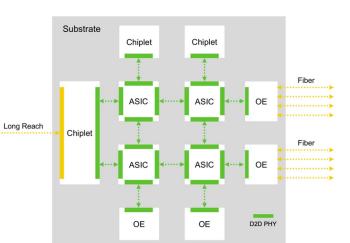

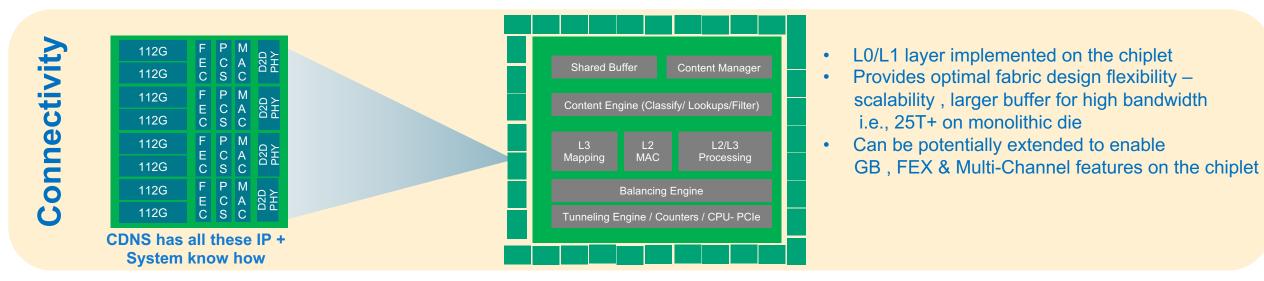

#### Heterogenous System : Chiplet IO Connectivity

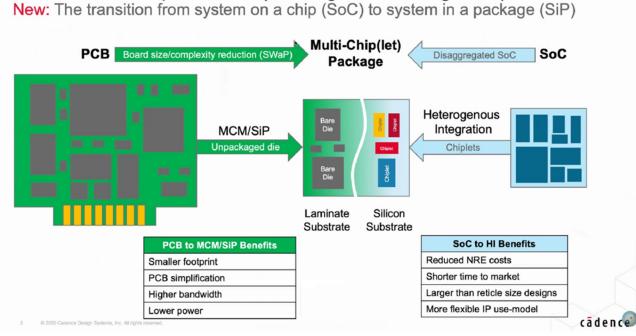

- Design partitioning is primary driven by "functional independence"

- Functional independence Lego Block Mindset, Repeatable & Scalable Architecture

- On of the key requirement for "Scalability" is IO Connectivity [Bandwidth]

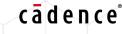

- This is legacy classic case of transitions from System Chiplet

SiP/MCM vs. Chiplet-Based (Heterogeneous Integration) Architectures

#### Classic Examples of Chiplet – IO Connectivity Dependency

| 112G | F P M DSD PHX                             |

|------|-------------------------------------------|

| 112G | E C A ZALA                                |

| 112G | FPM<br>D2D<br>PHX                         |

| 112G | E C A BAR                                 |

| 112G | F P A B P A P A P A P A P A P A P A P A P |

| 112G | E C A IZO<br>C S C                        |

| 112G | FPM<br>D20<br>PHY                         |

| 112G | E C A ZALA<br>C S C                       |

#### cādence°

### Chiplet Landscape (IO Chiplet - Connectivity)

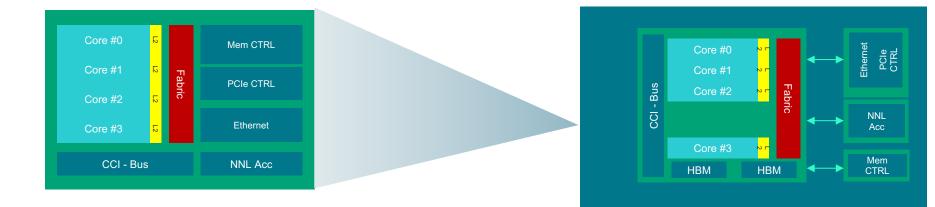

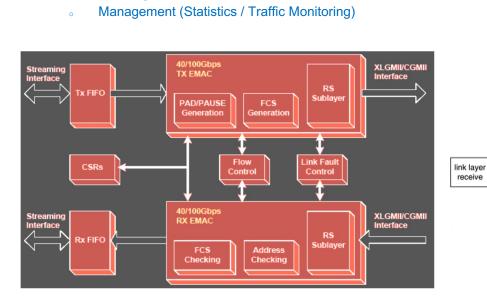

**Block Diagram**

cādence

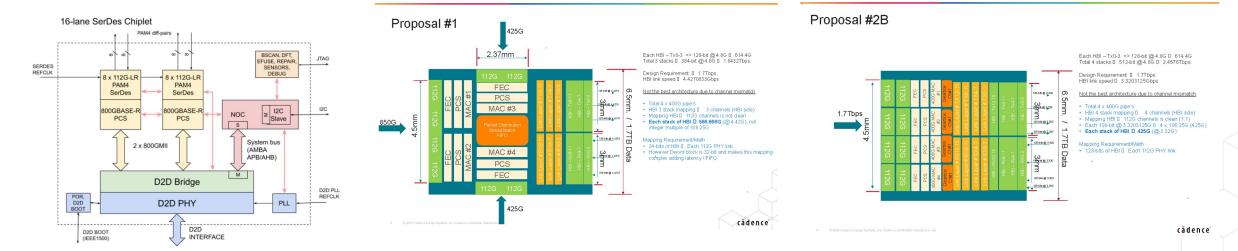

#### IO Tool Automation for Connectivity – Chiplet

- Primary factor for designing Connectivity IO Chiplet

- Architectural (MAC / PCS / Gearbox / Glue Logic)

- Physical/Electrical Constraints bandwidth , beach front , BER , latency , power , package

- Automation primary focus on the "Architectural" element considering the physical constraints as fixed constants (data-path connectivity only)

- Automation is agnostic towards any PHY being considered

- 。 BoW, OHBI, Ultra-Link, UCIe

- Only parameter necessary is the data-path (if provided would be beneficiary)

- Automation targets :

- Design Optimization (PPA)

- TTM (Scalability)

#### cādence°

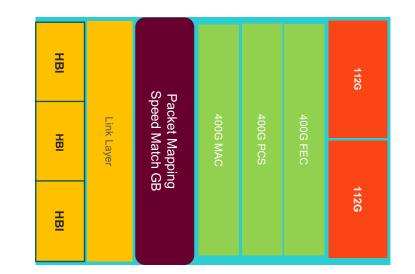

#### IO Connectivity Deep Dive – Chiplet

Focus is to optimize the L0/L1 connectivity on the chiplet – Scalable to be re-usable across different market segments / products

#### cādence°

# Automation Engine – Parameter for IO Chiplet (Connectivity)

1G/10G/25G/56G/112G/200G/400G/800G

Tunneling Protocol (RIoT / VXLAN / NVGRE..)

Channelized / Non-Channelized

MAC Engine

IFG

DMA

Filtering

SyncE (Timing)

Padding /Frame Length

Flow Control

**CRC Checks** Clocking

0

0

0

0

0

٠

- Packet Processing / Mapping •

- **Architectural Design**

- Based on customer/application requirement

ICMP error handling

IP

TTL

decrement

ARP

query

scheduler

link layer

transmit

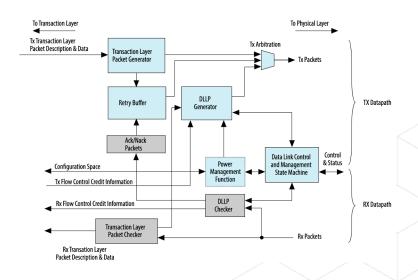

- Flow Injection / Header Checker

- Classifier / Scheduler

- **Network Rules**

IP header

check

classifier

receive

**Application Rules**

IP lookup

ARP

response

- Link Layer •

- Link Training (LTSSM)

- Data integrity mechanism

- **Retry Buffer**

- Packet Generator / Checker

- **Power Management**

- Arbitration

cādence

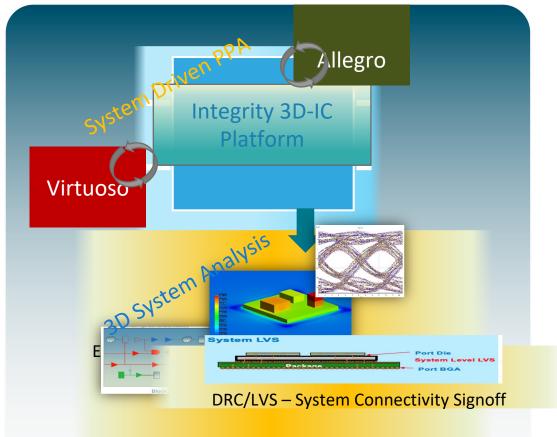

#### Cadence – Accelerating Chiplet Design

- Design Automation PAA (IP & Architecture)

- 3D-IC : Design Planning , Implementation & Sign-off

#### Integrated 3D Design Planning and Implementation

Comprehensive system enabling "System Driven PPA"

# Early 3D Thermal, Power & STA analysis

cādence

#### **Scaling Horizontally & Vertically**

# cādence

© 2022 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks of Cadence Design Systems, Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or trademarks of PCI-SIG. All other trademarks are the property of their respective owners.