# **48V 2-stage System Efficiency Optimization by using STC Converter with Dynamic Converting Ratio**

Sam Yang Associate Direct of Power Design Dept. Wiwynn

SOLUTION PROVIDER®

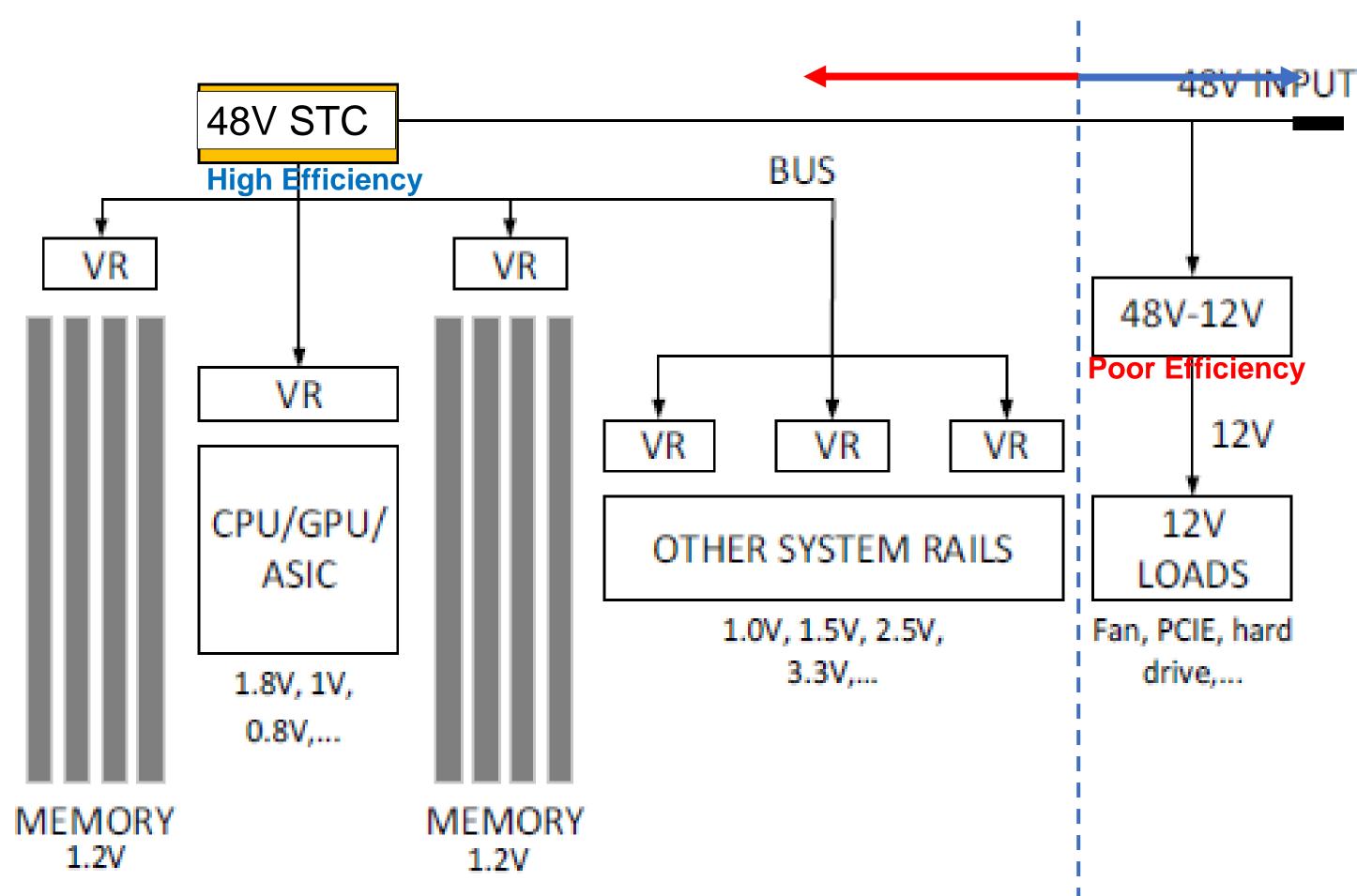

## 2-Stage Architecture for 48-to-Pol Power Delivery – Ratio Adjustable STC Converter

- enables high efficiency high density 48V 1<sup>st</sup> stage conversion in 2-stage architecture.

- - > High converting ratio for lower power application

- > Low converting ratio for higher power application

• Google's proprietary STC 48V Bus intermediate STC(Switched Tank Converter)

• To further optimize system efficiency over all the load range Wiwynn propose dynamically change STC converting ratio based on output power condition:

## 2-Stage Separate Efficiency Chart

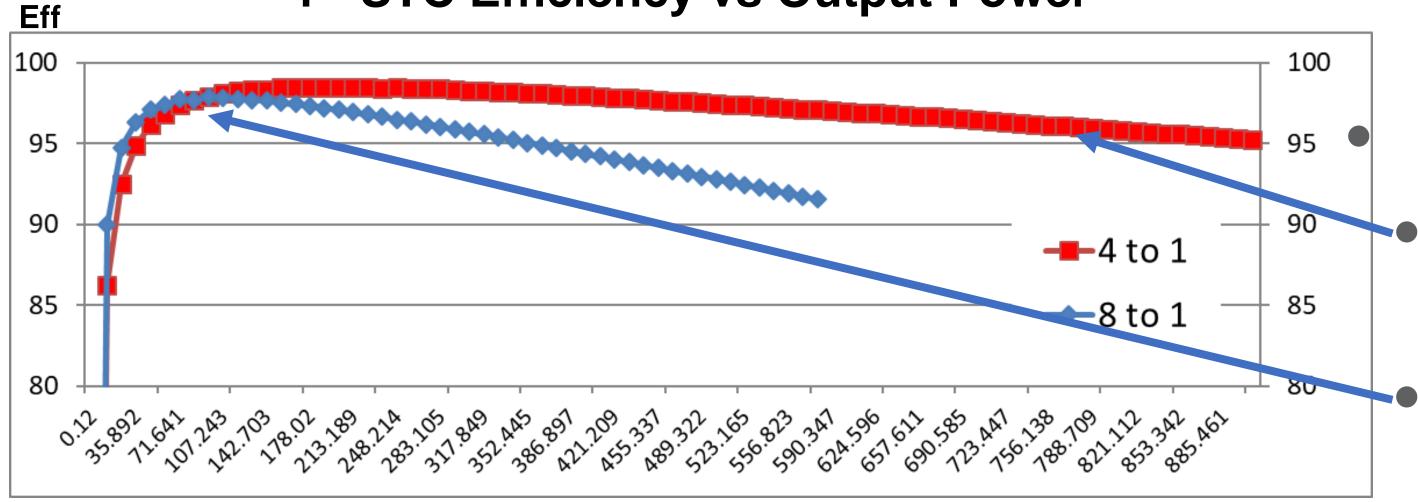

#### 1<sup>st</sup> STC Efficiency vs Output Power

SUMMIT

#### 1<sup>st</sup> stage STC eff:

- Higher eff with low converting ratio at high output power

- Moderate eff difference at lower load

- 2<sup>nd</sup> stage VR eff:

- Higher eff with lower Vin in light load

- Moderate eff difference at heavy load

OCP

мміт

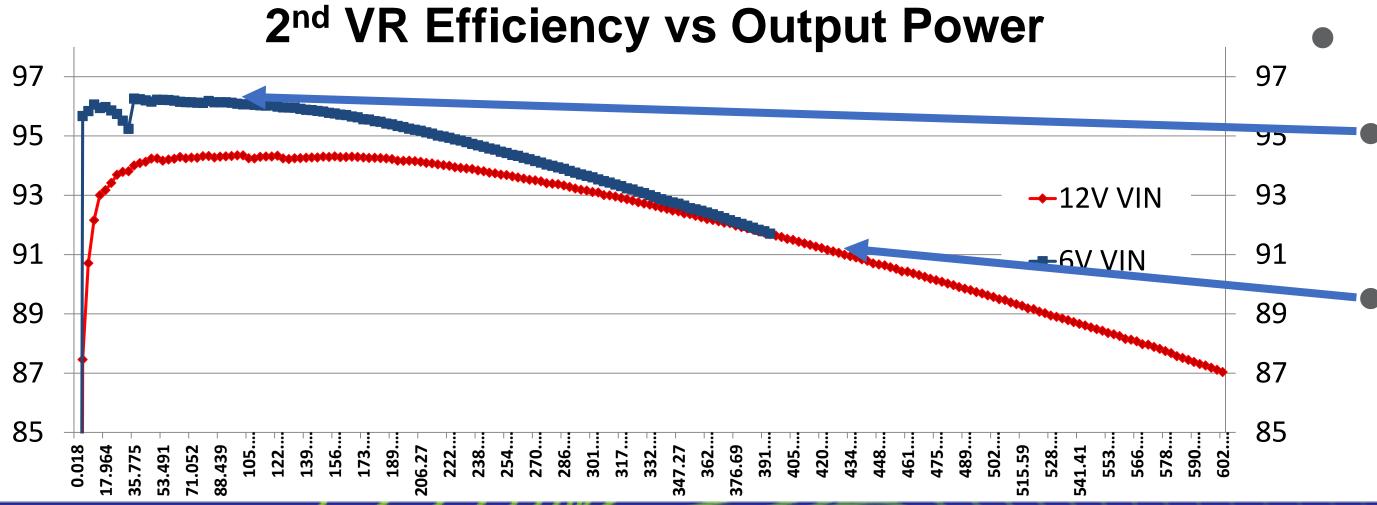

- Higher converting ratio gives better efficiency at lower load while reducing converting ratio can effectively gain higher efficiency at heavier load.

- With dynamic adjusted STC converting ratio, system efficiency can be optimized over all load range.

## **EV-board measurement data**

|  |     |           | lo_50A     |              | lo_100A    |           | lo_200A    |           | lo_300A    |           | lo_350A    |           |

|--|-----|-----------|------------|--------------|------------|-----------|------------|-----------|------------|-----------|------------|-----------|

|  |     |           | Efficiency | P_loss(W)    | Efficiency | P_loss(W) | Efficiency | P_loss(W) | Efficiency | P_loss(W) | Efficiency | P_loss(W) |

|  | 4:1 | 1st Stage | 97.889%    | 2.058        | 98.453%    | 2.798     | 98.114%    | 6.776     | 97.356%    | 14.207    | 96.917%    | 19.49     |

|  |     | 2nd Stage | 94.309%    | 5.545        | 94.298%    | 10.077    | 92.764%    | 25.436    | 90.185%    | 51.476    | 88.608%    | 89.437    |

|  |     | overall   | 92.318%    | 7.60         | 92.839%    | 12.89     | 91.014%    | 32.212    | 87.8%      | 65.683    | 85.876%    | 108.927   |

|  | 8:1 | 1st Stage | 97.86%     | 2.071        | 97.34%     | 4.792     | 94.877%    | 18.981    |            |           |            |           |

|  |     | 2nd Stage | 96.14%     | 3.693        | 95.623%    | 7.757     | 93.068%    | 24.454    |            |           |            |           |

|  |     | overall   | 94.075%    | <b>5.764</b> | 93.085%    | 12.549    | 88.3%      | 43.435    |            |           |            |           |

### Open. Together.

x

Microsoft Excel 工作表

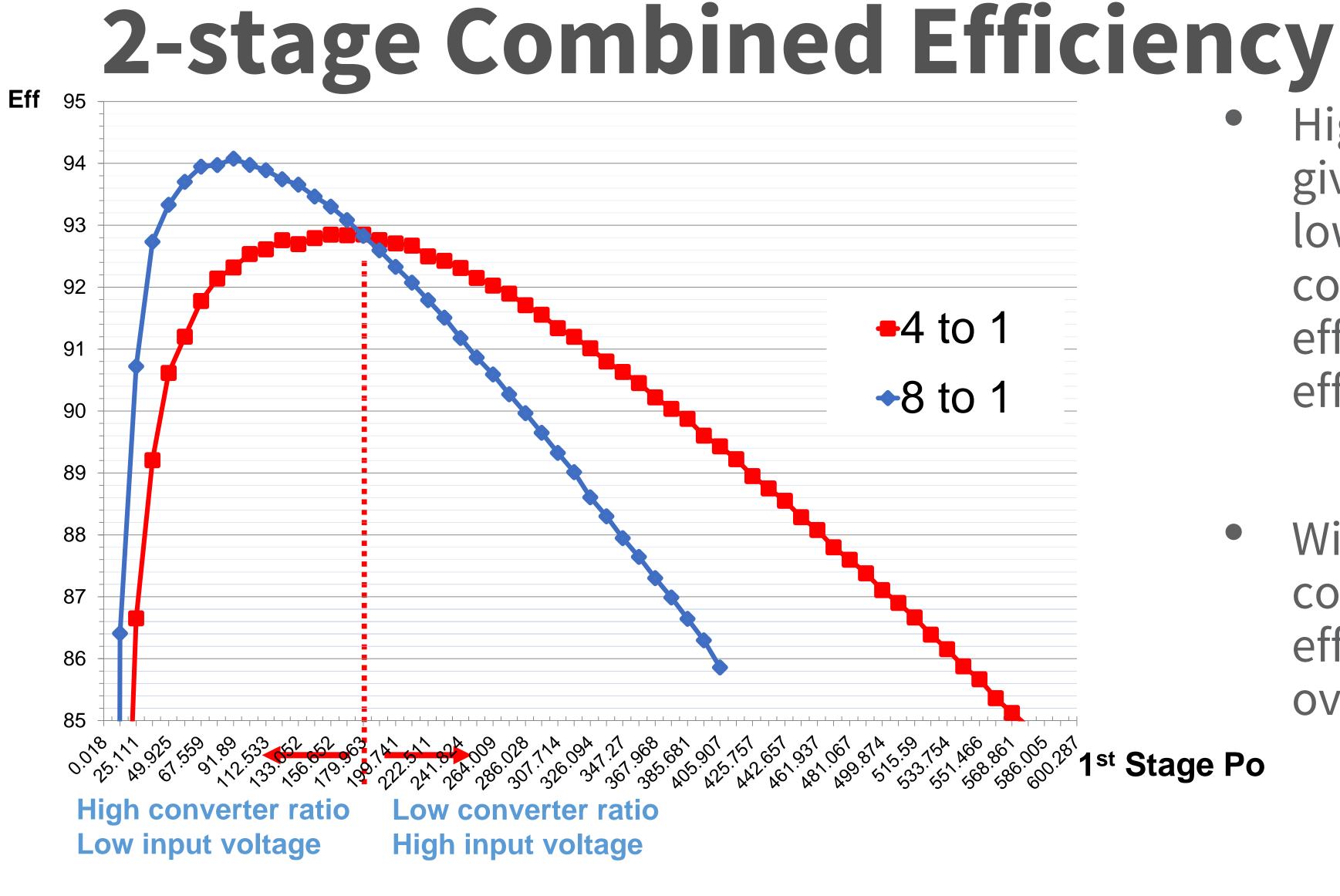

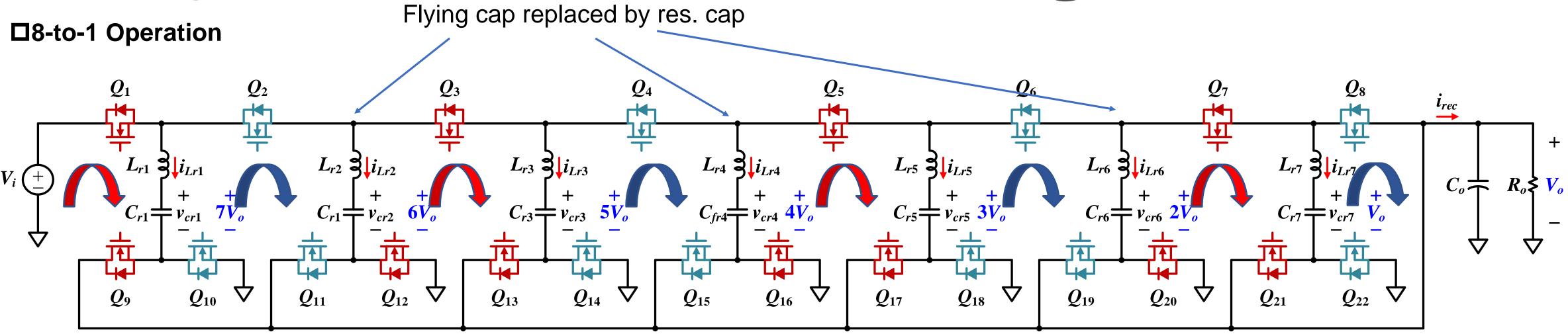

## **STC Circuit Converting Ratio 4 to 1**

- Q1, Q3, Q5, Q8 and Q9 turn on/off at the same time with 50% duty cycle.

- Q2, Q4, Q6, Q7 and Q10 are complementary signal for the remaining 50% duty cycle

- Cr1 and Cr2 are resonant capacitors with inductance constitute resonant tank

- Cf1 is DC flying capacitor with much lower voltage ripples.

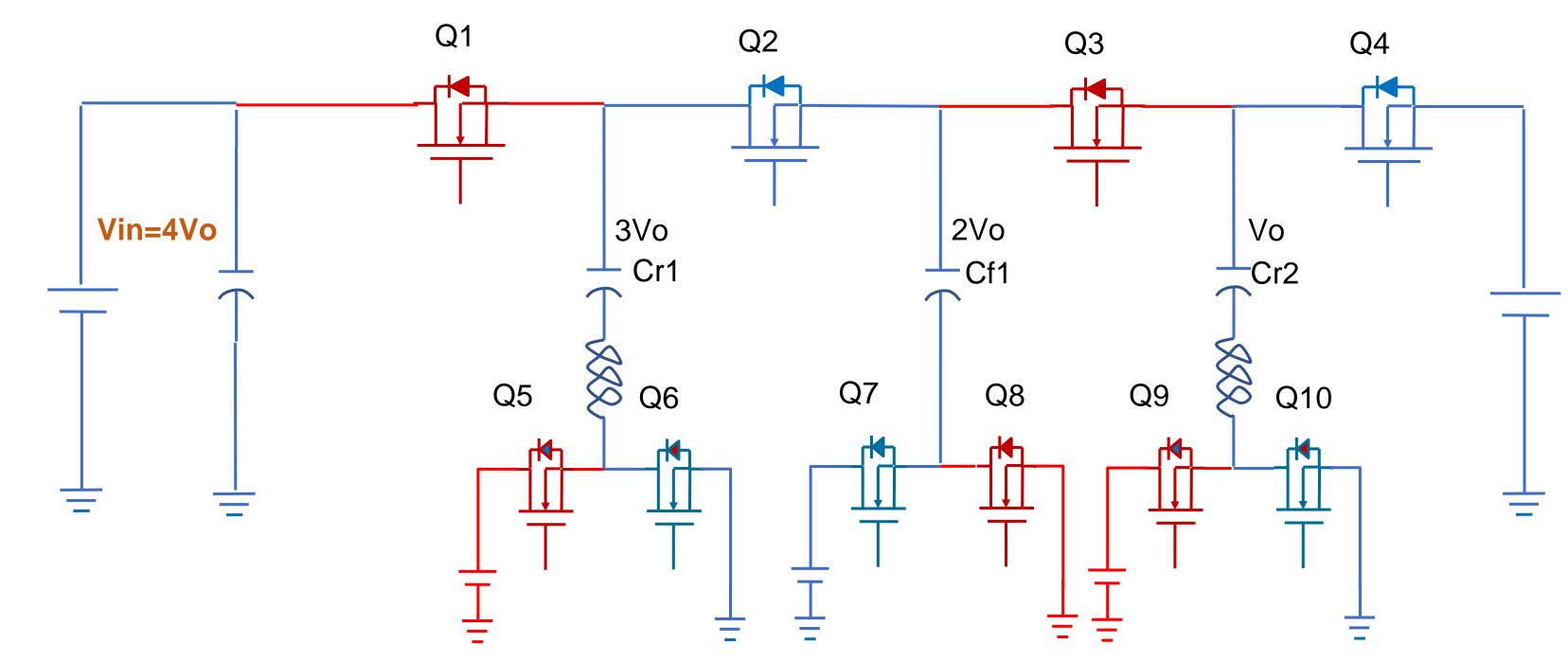

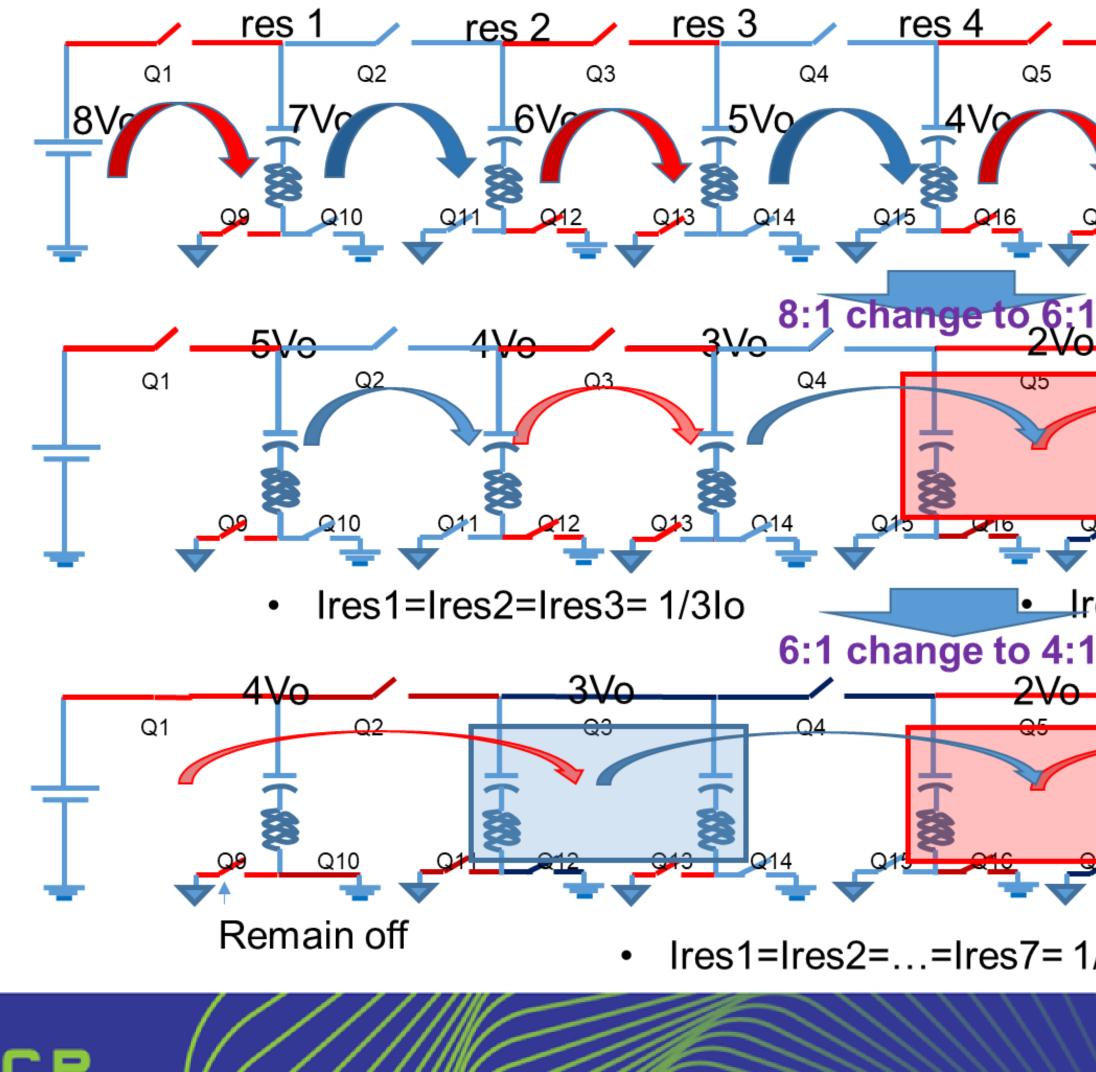

## **Adjustable STC Converting Ratio**

**Q4-to-1** Operation

Parallel resonant to step down the converting ration

UMMIT

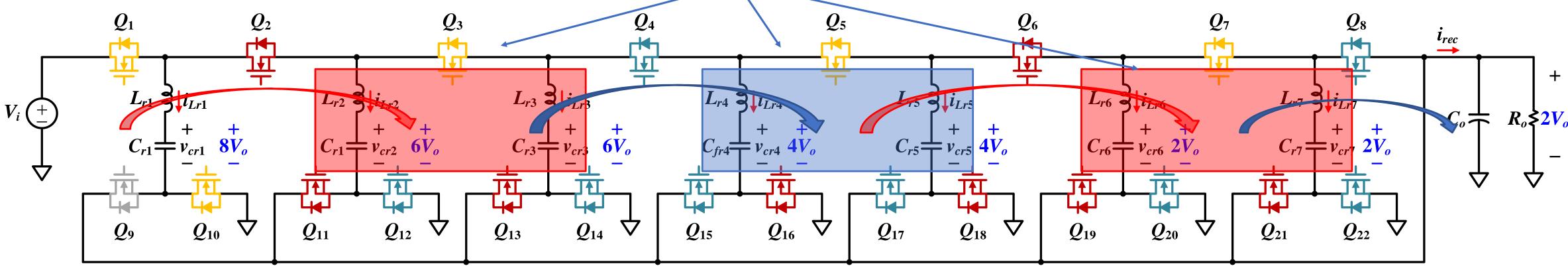

### **Resonant Current Comparison in 4:1 and Paralleled 4:1**

cut by half.

Resonant Freq keeps the same due to parallel operation.

Io is distributed in each resonant leg due to parallel operation, conduction losses is

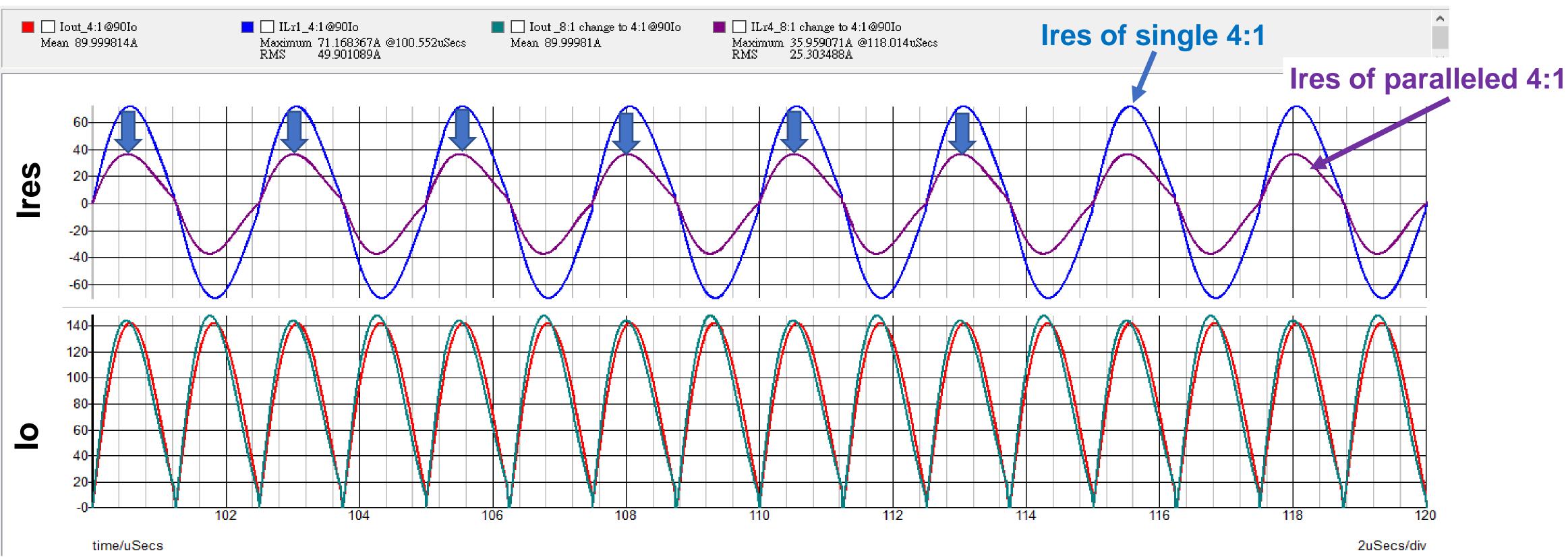

#### EV-Board Dimension 1.2KW Peak power

Main Switch MOSFET: 5.15\*5.95mm<sup>2</sup> Inductor: 5.7\*5.7mm<sup>2</sup> Half Bridge MOSFET: 3.2\*3.2mm<sup>2</sup>

| Component                    | PN                 | Comp   |

|------------------------------|--------------------|--------|

| Main switch 1                | BSC015NE2LS5I      | Infine |

| Main switch 2                | BSC022N04LS6       | Infine |

| Driver                       | 2EDF7275K          | Infine |

| HB                           | BSZ011NE2LS5I      | Infine |

| Choke                        | BPMIWN06068032NK0E | Chilis |

| DSP controller               | F28035             | TI     |

| Resonant Cap1,<br>100V 2.2uF | SC2D2U100V6KX-1    | Murat  |

| Resonant Cap 2,<br>100V 1uF  | SC1U100V5KX        | Murat  |

| Resonant Cap 3,<br>50V 2.2uF | SC2D2U50V6KX-4     | Murat  |

| Resonant Cap 4,<br>50V 1uF   | CL21B105KBFNNNE    | Sams   |

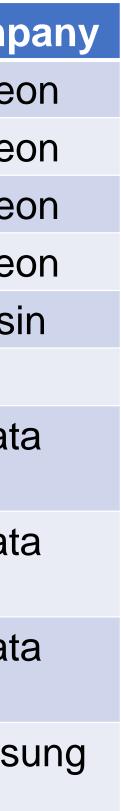

# Developing Roadmap

## Summarize

- converting ratio based on power requirement

- stress in heavy load

- Future work:

- Looking for integral solution for ZCS exact switching timing.

- Define converting ratio switching point and hysteresis

#### STC employ LC resonant tank to realize high efficiency DCDC power conversion for 2 stage 48V system, flexible converting ratio can further improve 2-stage overall efficiency by dynamically alter

• High converting ratio reducing 2<sup>nd</sup> stage VRs voltage stress in lower load

• Low converting ratio and parallel resonant legs to reduce 1<sup>st</sup> stage current

Simplified main switches driver design and reduce choke/board size.

## Question?

# Open. Together.

#### OCP Global Summit | March 14–15, 2019

## Appendix

## Google's 48V 2-Stage Conversion Approach

- STC enables high efficiency 2-stage conversion, more 2<sup>nd</sup> stage VRs supported by STC, higher board efficiency is.

- Current Design Targeting 600W for STC 48V to VR with different converting ratio

- 4:1(Intel)

- 8:1(google)

- With increasing CPU/DDR power, higher STC power is needed

#### **Converting Ratio Changes**

#### res 5 res 7 res 6 res 4 Q5 Q6 Q7 Q8 3V/a Vo Q18 Q17 Q19 Q16 Q6 Q8 QT Vo Ires4=Ires5=Ires6=Ires7= 1/6Io 6:1 change to 4:1 2Vo <del>Vo</del> Q6 Q8 Vo

Ires1=Ires2=...=Ires7= 1/4 Io