# 0 CHIPLET CREATION PLATFORM - ACCELERATED **DESIGN EXECUTION AND CROSS COMPLIANCE**

Robbie Adler, Animesh Mishra Chassis Engineering, Test Chips and Discrete Devices Chipset and IP Group, IPSG

O

OCP/ODSA Workshop June 10, 2019

## **LEGAL INFORMATION**

This presentation contains the general insights and opinions of Intel Corporation ("Intel"). The information in this presentation is provided for information only and is not to be relied upon for any other purpose than educational. Statements in this document that refer to Intel's plans and expectations for the quarter, the year, and the future, are forward-looking statements that involve a number of risks and uncertainties. A detailed discussion of the factors that could affect Intel's results and plans is included in Intel's SEC filings, including the annual report on Form 10-K.

Any forecasts of goods and services needed for Intel's operations are provided for discussion purposes only. Intel will have no liability to make any purchase in connection with forecasts published in this document. Intel accepts no duty to update this presentation based on more current information. Intel is not liable for any damages, direct or indirect, consequential or otherwise, that may arise, directly or indirectly, from the use or misuse of the information in this presentation. Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

Copyright © 2019 Intel Corporation.

Intel, the Intel logo, are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others 2

ntel"). The ed upon for any ans and ts that involve a ect Intel's results . iscussion orecasts on more current therwise, that sentation. Intel e enabled

## GUALS

- Accelerated Creation

- Abstract away/package I/O (chiplet2chiplet) interface

- Enable "reasoning" about how to integrate value add ip "subsystems" into a standard "chassis" that include the C2C

- Chiplet packaging and IO treated as constraints

- Easy Composability and Validation of chiplet-based design

- Not limited to just design needed for all domains required to build chiplet – front end + back end HW design, SW sim environment, ported Sys FW/SW

## ... DELIVER DELIGHT TO CUSTOMER

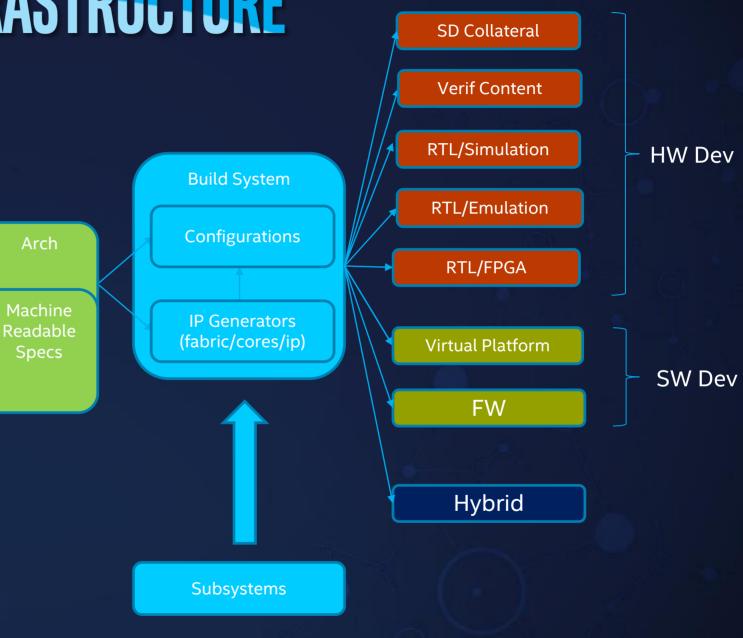

## **DESIGN INFRASTRUCTURE**

- Architecture + Machine readable Specs Input to the system

- Collection of Subsystems

- N "Chassis" Subsystems are always present

- IP Subsystem(s)

- Enables Consistent HW and SW Model and Collateral Output

- Hybrid Capabilities enable crossproduct mix-match of VP/EMU/FPGA

## WHAT'S A SUBSYSTEM

- A Subsystem abstracts the logical components that are required for an • architectural function and packages them for a correct and complete integration for all aspects required to build/design the final SoC

- Example: Controller IP + PHY, Clocking, Primary Fabric

- All of the pieces needed for all aspects of integration are included in the Subsystem Package:

- Example: Register Descriptions; Compilation Instructions; Power Intent (UPF); \_ Syn collateral

- C2C interface becomes a Subsystem "on the shelf". Standardizes on interface to enabled value-add IP to concentrate on its value-add

## **VIRTUAL PLATFORM**

### SW Accurate SystemC IP Models

Interconnect and Memory Map Model Virtual Platform

**Core Instruction Set Sim**

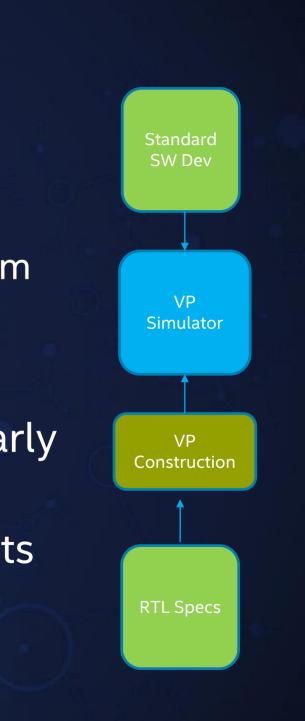

## **CONSISTENT VIRTUAL PLATFORM (VP)**

- Automatically assembled to ensure RTL and VP are consistent by construction

- VP Model and System FW assembled/generated by system

- Provides same debug environment as final FPGA/SOC ensuring consistency of SW dev/debug

- Deliverable to customers for integration testing and early development of SW/FW

- Easy path to Hybrid (VP +EMU/FPGA) Sim environments

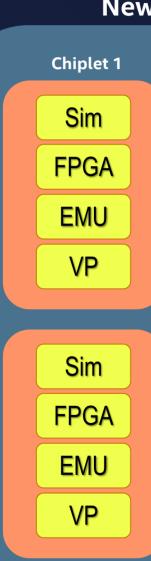

## **CHIPLET COMPOSABILITY**

- New Design is composed of new and existing Chiplets

- Design Infrastructure gives ability to design and verify new Chiplet

- Also need to design/verify the composed design before we spend \$\$\$ and time

- New VP + existing VPs enable early SW dev and lost cost dev vehicle

- New VP + existing EMU/FPGA in hybrid

- New FPGA/EMU + existing FPGA/EMU

Chiplet 3

### **New Design**

| Chiplet 2 |  |

|-----------|--|

| Sim       |  |

| FPGA      |  |

| EMU       |  |

| VP        |  |

|           |  |

| Sim       |  |

| FPGA      |  |

| EMU       |  |

| VP        |  |

| Chiplet 4 |  |

## CALL TO ACTION -> ADOPTION OF STANDARDS - KEY TO SCALE AND SUCCESS

### **STANDARD TFM - REDUCED TTM - > CUSTOMER SUCCESS**

## **PROVEN SUCCESS OF CHASSIS INTEGRATION AND EXECUTION**

## **CROSS COMPLIANCE - ROBUST AND TRUSTED VALIDATION**

## **CONSISTENT VP - ENABLE EARLY MODELING**

**SUMMARY & CONCLUSION**