### ODSA

## Protocols over Die-to-Die Interfaces

David C. Kehlet, Research Scientist, Intel Corporation

## Legal Information

This presentation contains the general insights and opinions of Intel Corporation ("Intel"). The information in this presentation is provided for information only and is not to be relied upon for any other purpose than educational. Statements in this document that refer to Intel's plans and expectations for the quarter, the year, and the future, are forward-looking statements that involve a number of risks and uncertainties. A detailed discussion of the factors that could affect Intel's results and plans is included in Intel's SEC filings, including the annual report on Form 10-K.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at www.intel.com.

Results have been estimated or simulated using internal Intel analysis or architecture simulation or modeling, and provided to you for informational purposes. Any differences in your system hardware, software or configuration may affect your actual performance.

<sup>†</sup>Tests measure performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit www.intel.com/benchmarks.

Copyright © 2019 Intel Corporation.

Intel, the Intel logo, the Intel. Experience What's Inside logo, eASIC, and Stratix are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others

## Contributors and Collaborators

Jaideep Dastidar – Xilinx

Kevin Drucker – Facebook

Quinn Jacobson – Achronix

Peter Jenkins – Avera Semi

Brian Kahne – NXP

David Kehlet – Intel

Mark Kuemerle – Avera Semi

Paul Mattos – Avera Semi

Dimitry Melts – Facebook

Gary Miller – NXP

Millind Mittal – Xilinx

Mats Myrberg – Microsoft

Bapi Vinnakota – Netronome

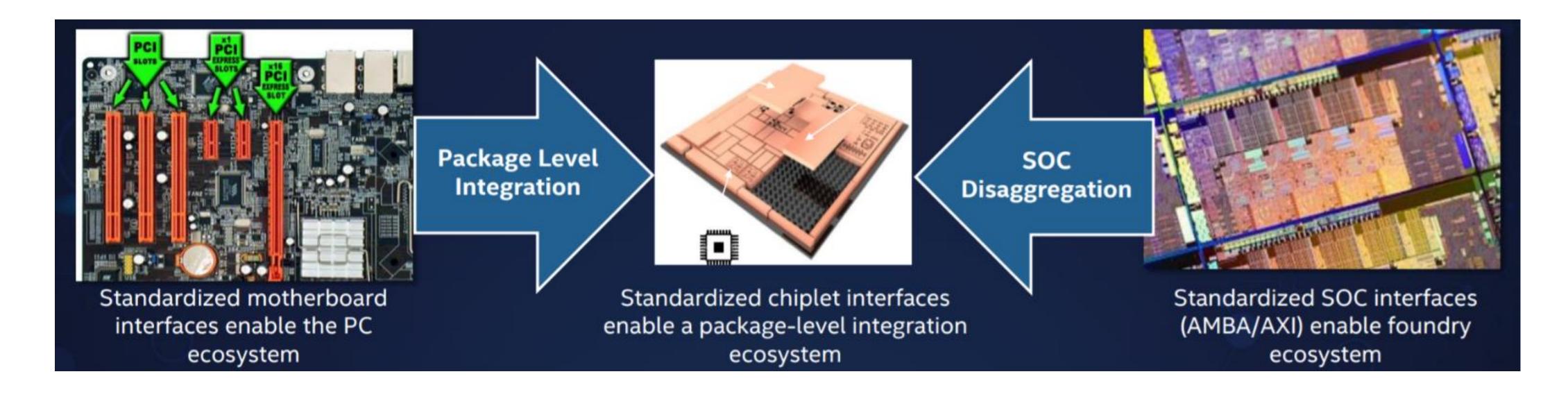

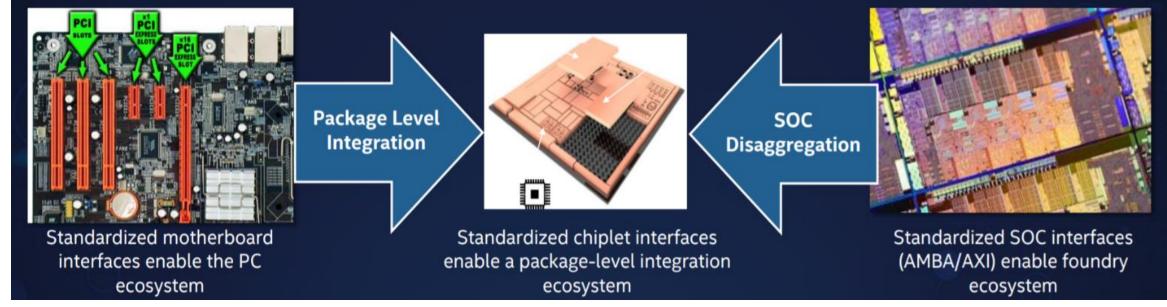

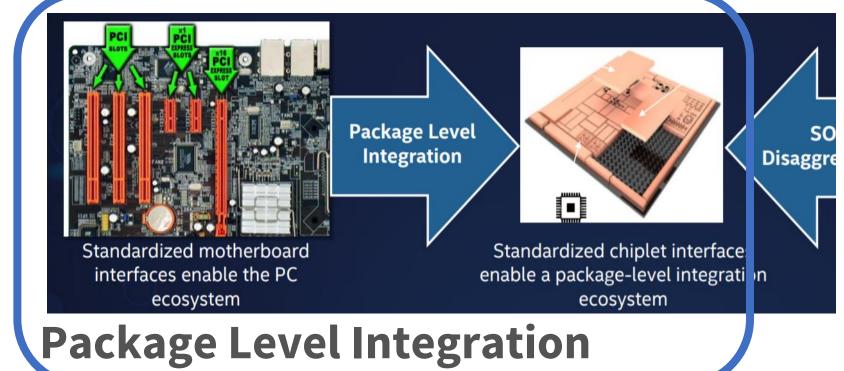

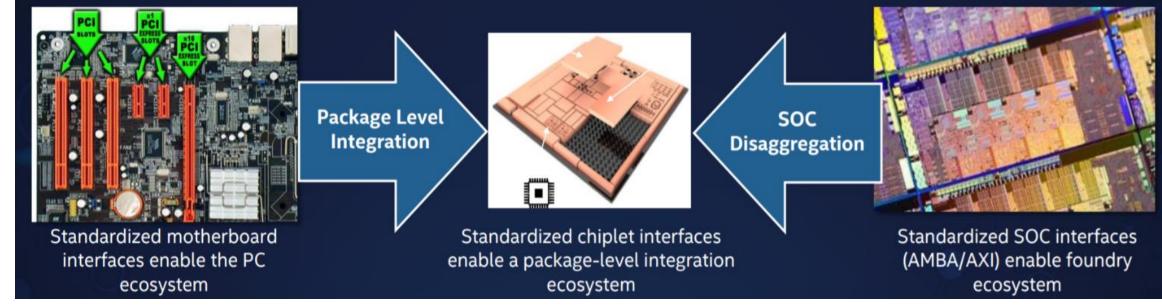

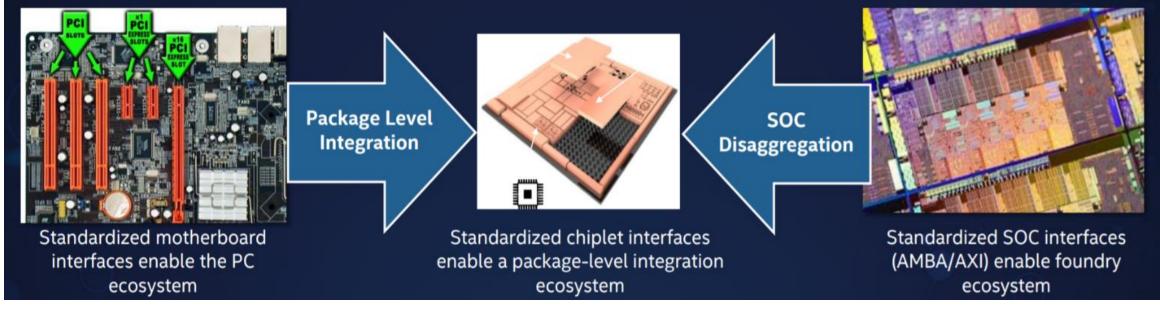

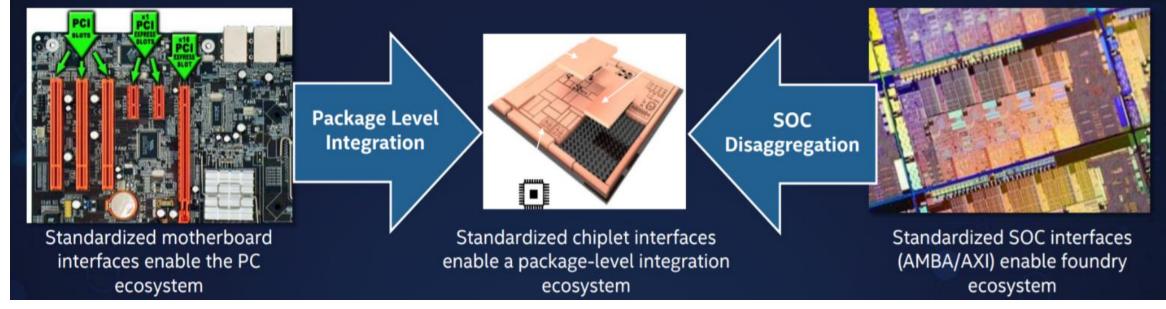

## Two Broad Use Cases

Package Level Integration

**SOC Disaggregation**

Use cases drive protocols!

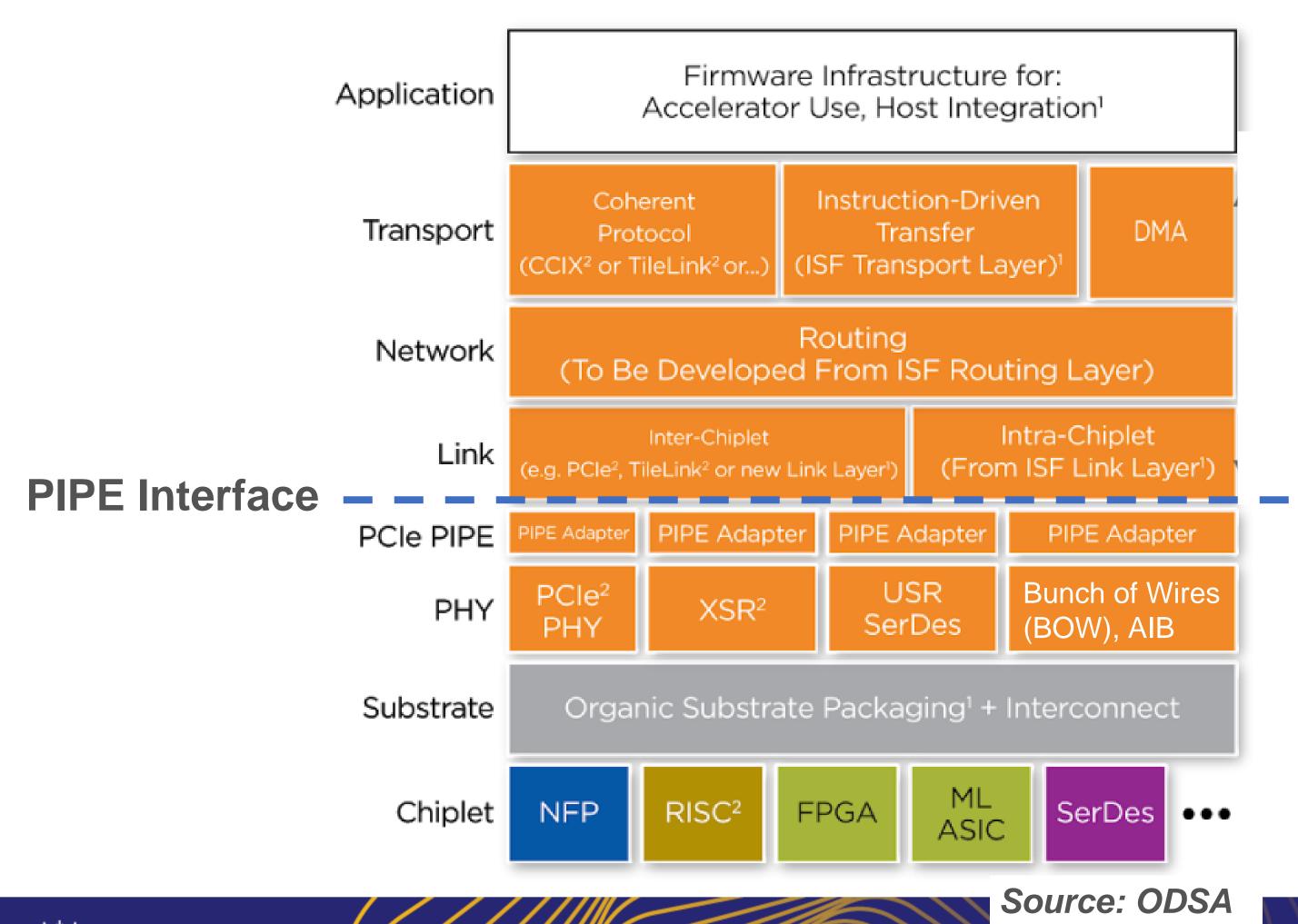

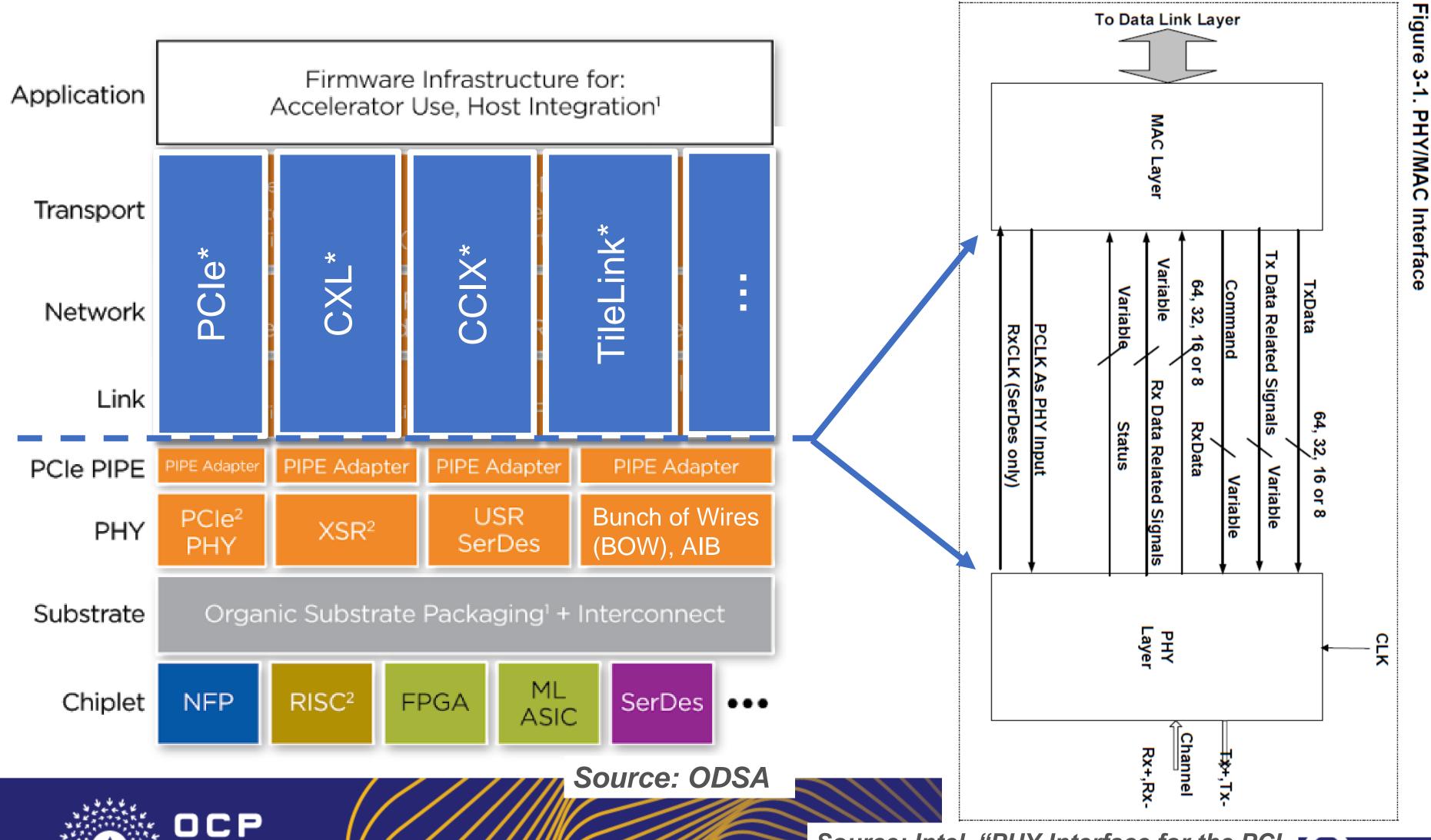

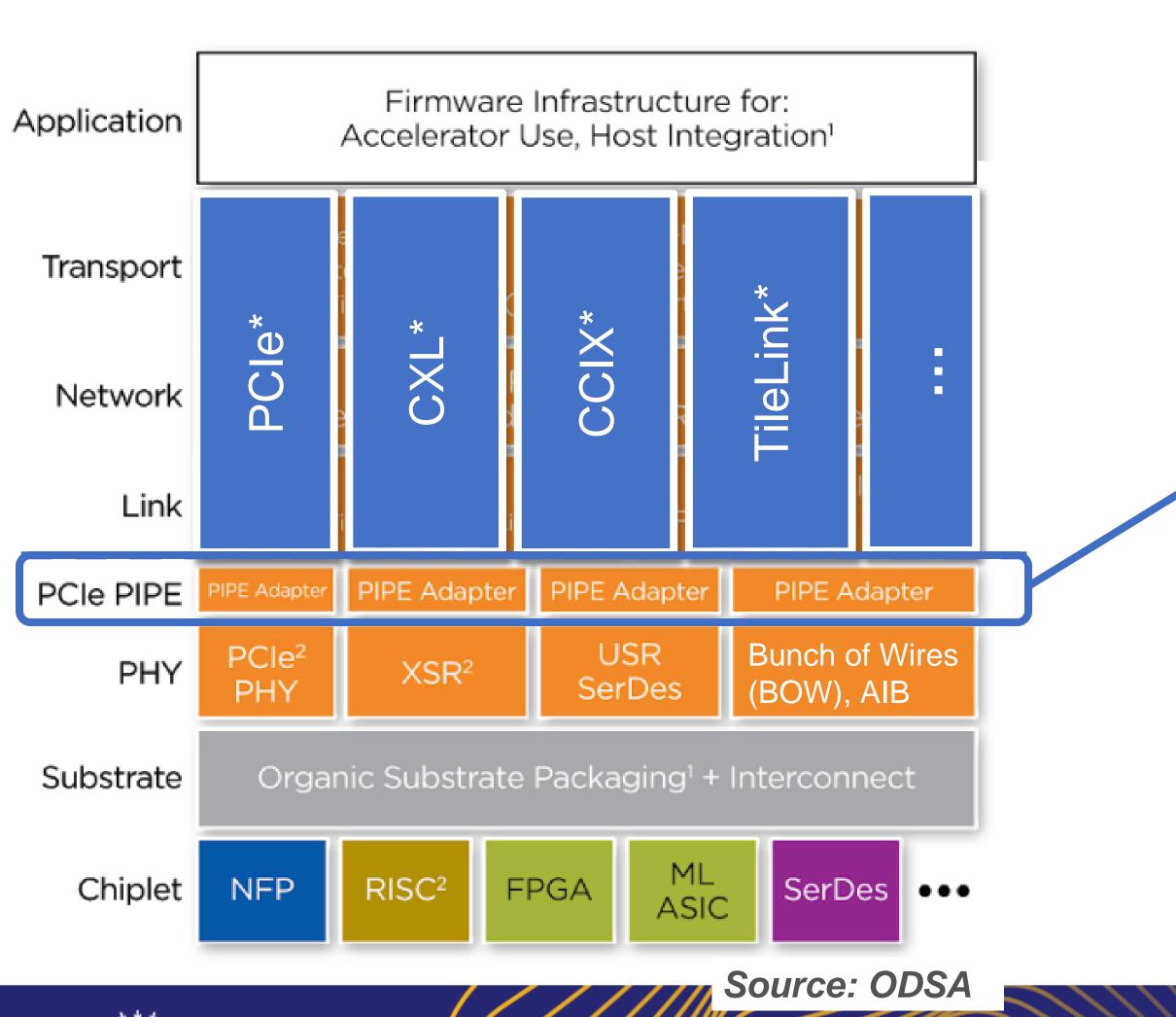

# Protocols for Two Broad Use Cases

### Package Level Integration

- Commonly attached to CPU

- Currently PCIe boards

- Developers want a coherent memory model

- Examples: CXL\*, CCIX\*, OpenCAPI\*

- Consortia already in place here

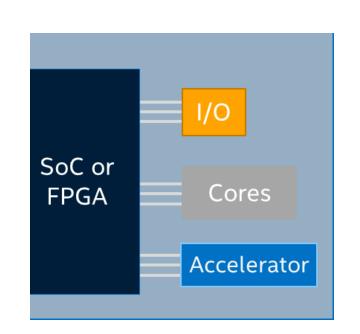

### SoC Die Disaggregation

- Currently on die module-to-module

- ASIC developers like their AXI\*-style lightweight protocols

- Examples: AXI\* Streaming, AXI4\* (Memory Mapped)

**Package Level Integration**

**SOC Disaggregation**

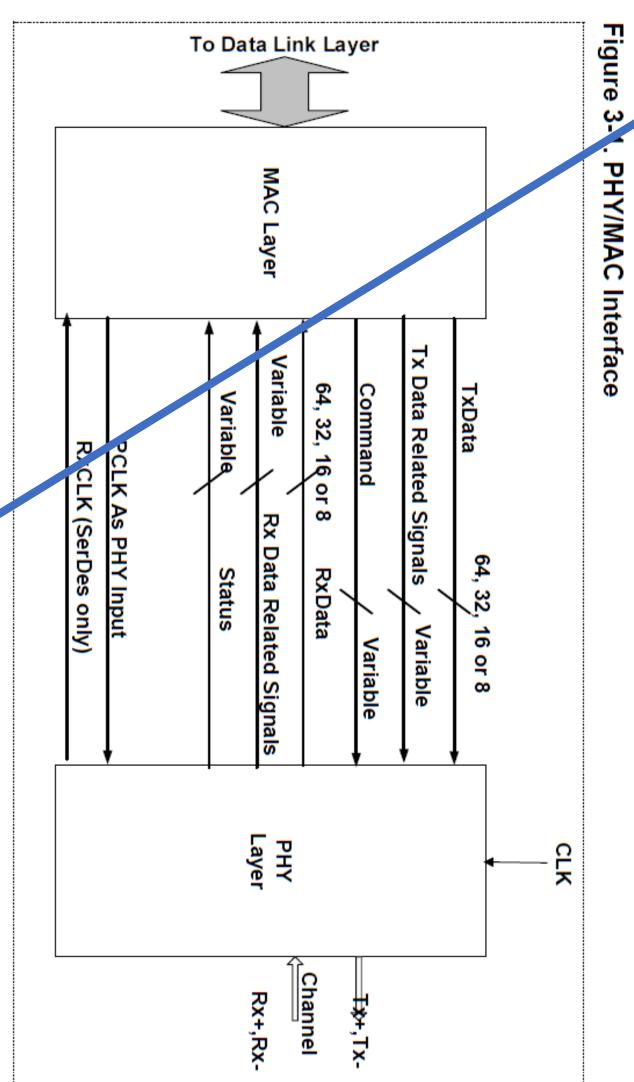

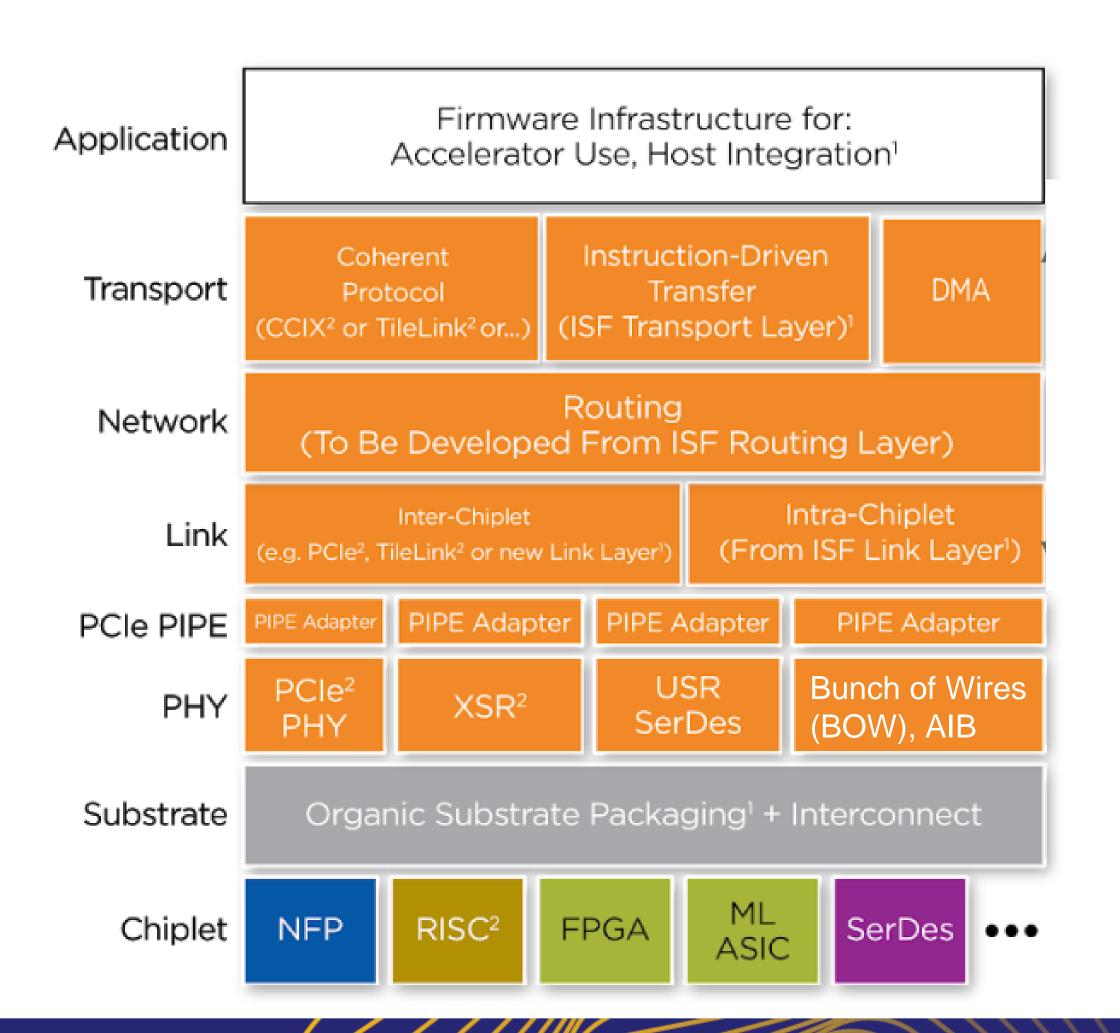

Source: Intel, "PHY Interface for the PCI

Express, SATA, USB 3.1, DisplayPort

and Converged IO Architectures"

**PIPE Adapter**

- Standard PIPE

Interface follows PIPE

Specification

- Adapter converts

PIPE to native PHY

interface (e.g. AIB,

BoW, SERDES).

- Often PHY provider creates the PIPE adapter code.

- Upper stack to PIPE (PCI Express, CCIX, CXL) can be used asis!

Source: Intel, "PHY Interface for the PCI Express, SATA, USB 3.1, DisplayPort and Converged IO Architectures"

# SoC Die Disaggregation Protocols

Strong preference towards using existing protocols

• Examples: AXI4, ACE, CXS, AXI Streaming

### **Evaluation Criteria**

- Functional Requirements

- E.g. Transaction ordering, Virtual channels, Error detection or correction, Data rates

- Throughput & Efficiency

- Latency

- Implementation Complexity

- E.g. Flow control, retry/replay, CRC

- Adoptability (Current Usage)

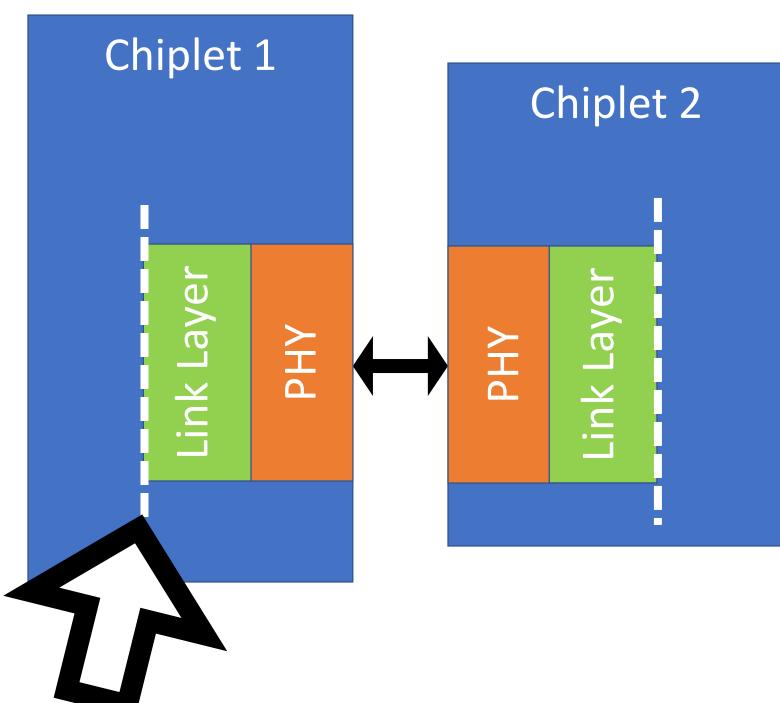

Goal: Define the boundary between the Blue and Green (Link Layer to rest of the chiplet functions)

# SoC Die Disaggregation Protocols

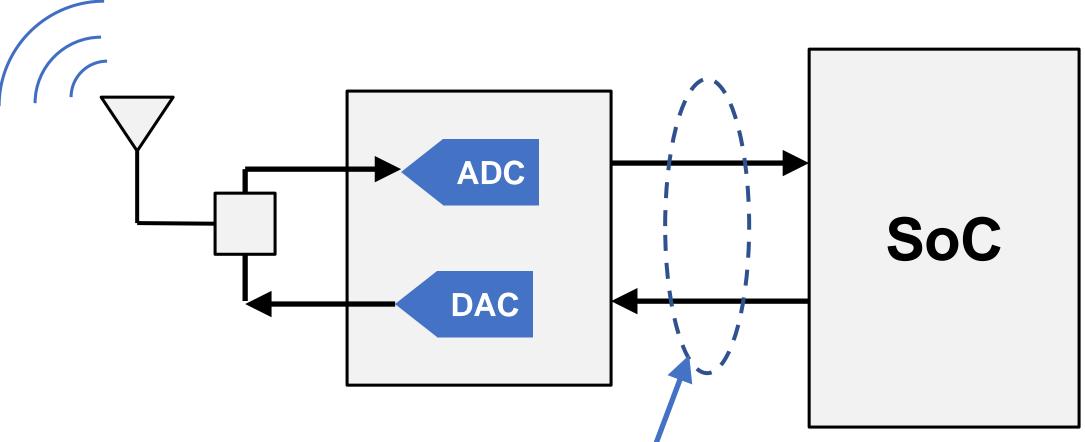

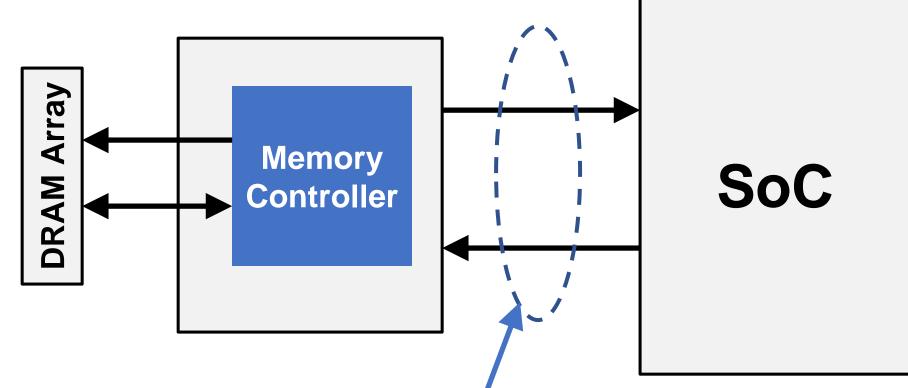

Ideal protocol characteristics:

- Transfer rate linked to the sample rate (common clock reference), no gearboxing

- Data arrives every clock

- Low latency

- Simple convention on samples within a flit

Ideal protocol characteristics:

- Looks like AXI4 (Memory Mapped) to my SoC

- Efficiently multiplexes my SoC's reads & writes

- Low latency

- Memory clock asynchronous to the transfer clock

→ SoC die disaggregation needs more than one protocol!

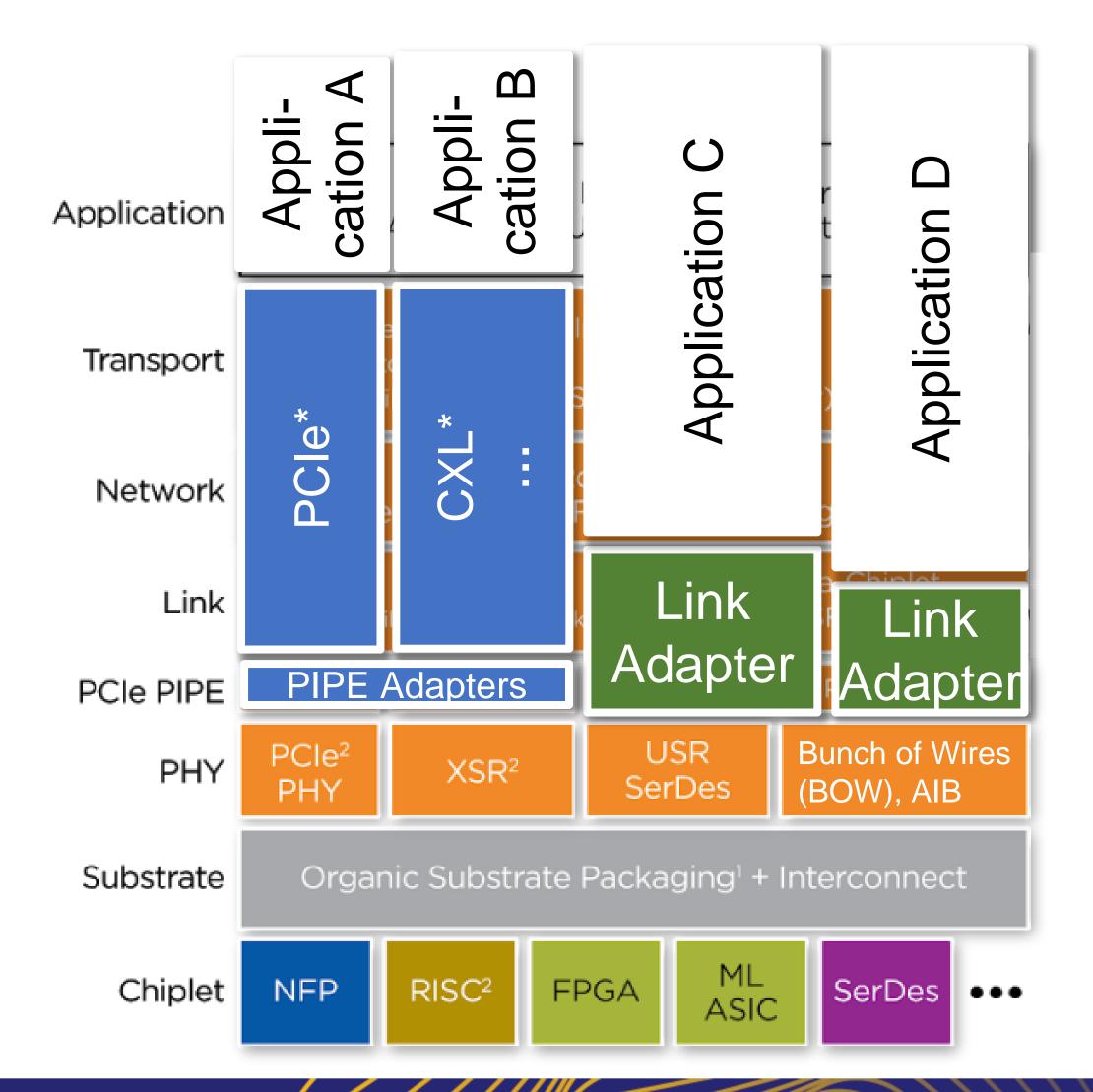

## Two Different Stacks

**Package Level Integration**

**SOC Disaggregation**

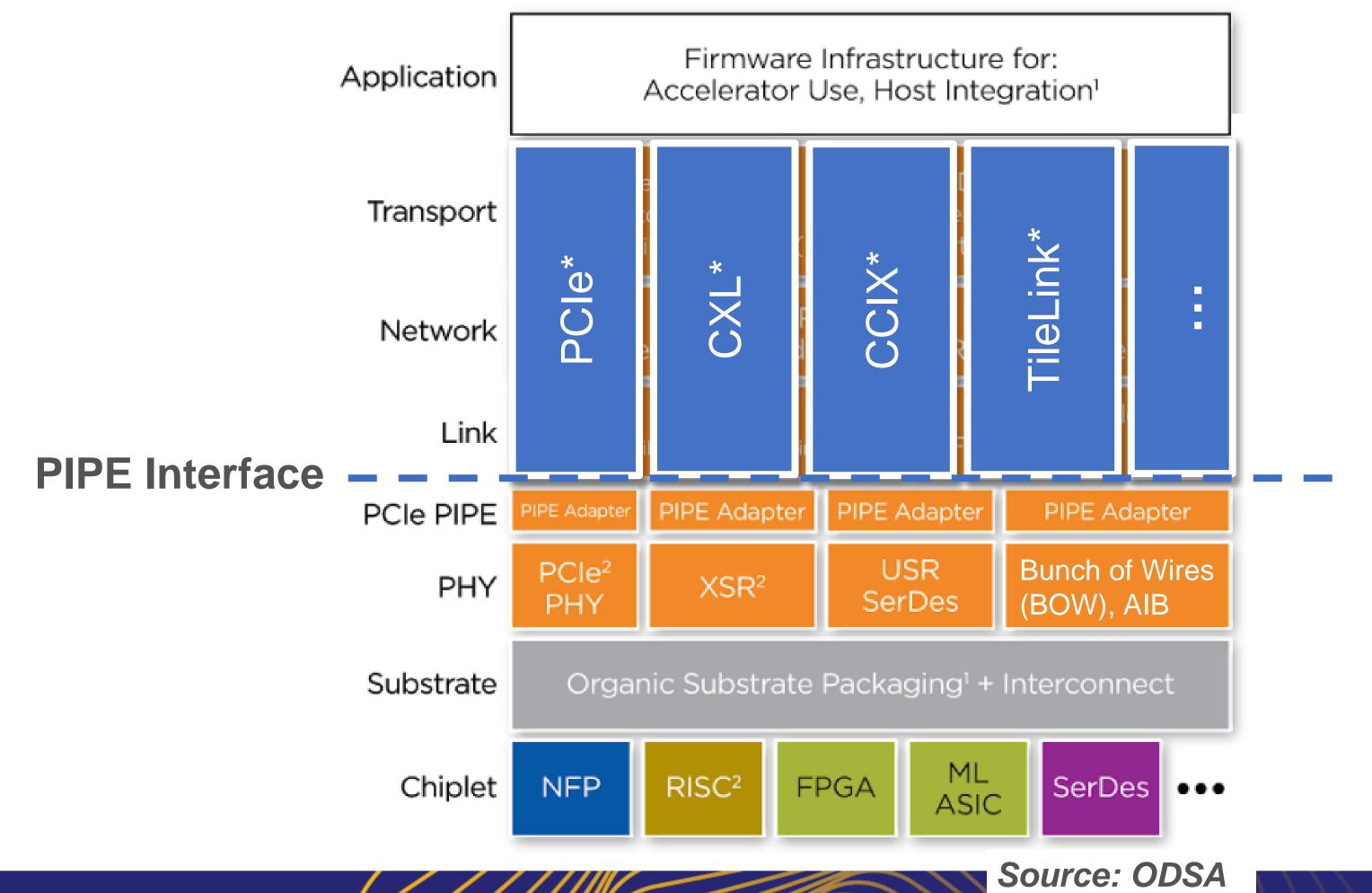

### Package Level Integration

- PIPE gives us a low-level interface that can support multiple existing protocols that have adopted PIPE

- With PIPE, we get PCIe\*, CXL\*, CCIX\* Gen-Z\*, SATA\* provide plug and play integration

### SoC Disaggregation

- Innovation here is at the PHY: AIB, BoW, XSR

- Near-monolithic performance (close to on-die module to module) is critical: low latency, high bandwidth, low power

- → Package Level Integration and SoC Disaggregation need different protocols

### Protocols

Package Level Integration

**SoC Disaggregation**

#### Package Level Integration Protocols

- Often incorporate a CPU

- Common PIPE interface

#### SoC Disaggregation Protocols

- Protocol Link Layer adapter to the PHY

- Protocol Link Adapters have different features matching the applications

### Protocols

Package Level Integration

**SoC Disaggregation**

Package Level Integration Protocols

- Often incorporate a CPU

- Common PIPE interface

SoC Disaggregation Protocols

- Protocol Link Layer adapter to the PHY

- Protocol Link Adapters have different features matching the applications

## Summary

"ODSA aims to define an open interface such that chiplets from multiple vendors that support the interface can be assembled into domain-specific products." – Bapi Vinnakota

- ODSA is tackling protocols for chiplets

- Contact us if you'd like to contribute!

- david.kehlet@intel.com

- bapi.vinnakota@netronome.com