# Open Domain Specific Architecture

Bapi Vinnakota Sub-project lead representing an active community of contributors from over 25 companies

Broadcom

### Outline

- Introduction to the ODSA

- Activities, results and roadmap

- We need your help!

# End of Moore's Law => Accelerators

**Domain-Specific for Machine Learning and Al**

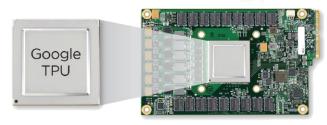

#### **Google TPU vs. CPU and GPU**

Source: "An in-depth look at Google's first Tensor Processing Unit (TPU)," Google Cloud, May 2017

- Server-attached devices for compute-intensive workloads

- Programmable, not hardwired, tailored to a domain

- 5-10X power performance improvement

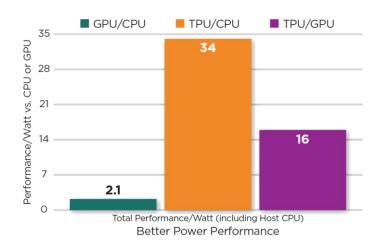

- Challenge: ASIC

development costs for a

targeted market

ASIC development costs

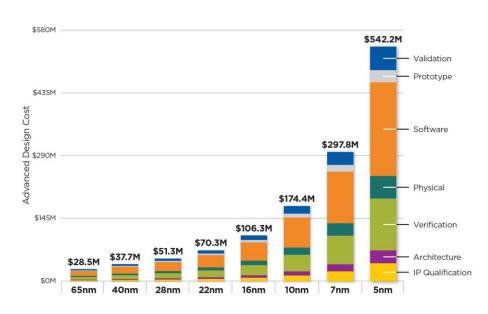

# Chiplets

- Create an integrated product across multiple die

- Optimize a function for a process node

- Economical approach to large die

- Reuse IP as hard IP

- Need a die-to-die interface, physical and logical

- Physical optimized for on-package

- Logical need a protocol

- Today: <u>proprietary vertically integrated D2D</u> <u>interfaces</u>

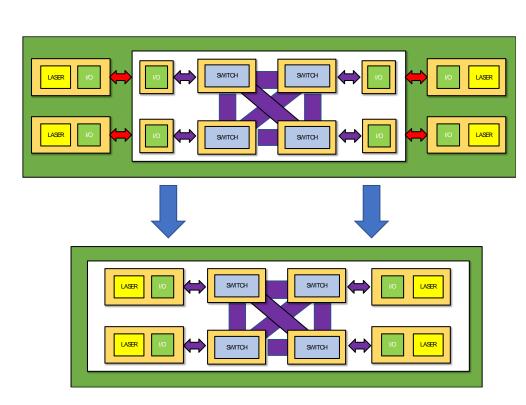

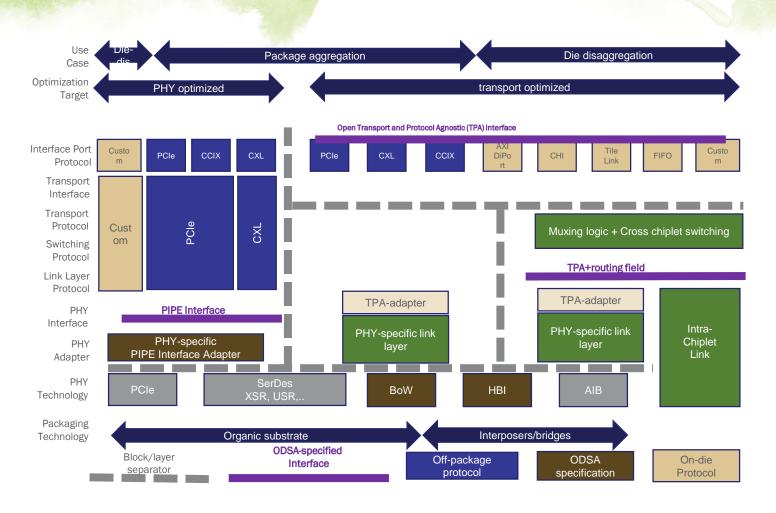

# ODSA D2D Interface

### Open with abstraction layers

- Open logic, Open PHY evolve separately

- Reuse protocols, minimize "new"

- Multiple options to make chiplets, market will choose

### **ODSA Charter**

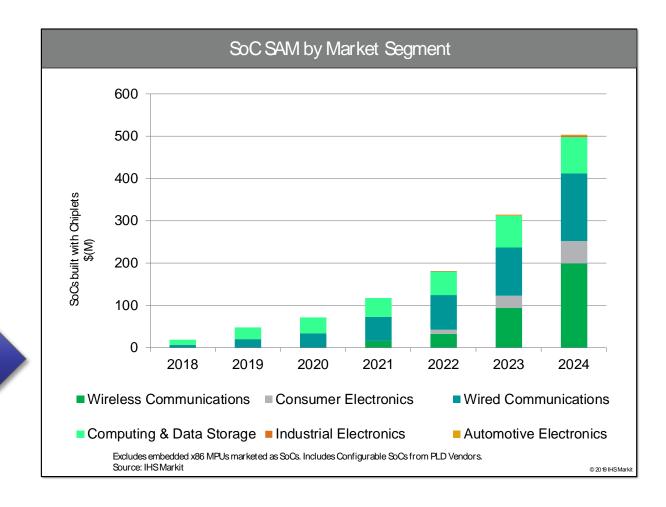

### Transformative Market Opportunity: The Tip of the Spear

- Independent research from IHS Markit

- Four (4) segments for chiplets analyzed (SoCs, MPU, GPU, PLD (FPGA/CPLDs)

- Six Verticals (wireless, wireline, consumer, computing, industrial, automotive)

#### **Subset of IHS Markit Data:**

- System on a Chip (SoC) segment

- **Conclusion**: Immediate opportunity for chiplets and an open interface

Tip of the spear !!!

## Attendees and Participants:

Attendance and/or participation do not imply corporate endorsement

Tools, Manufacture, Design, Test, Integration

Systems vendors, End users, ISVs, Service Providers

Started 11/2018 with 7 companies

Started as an Open Compute Project activity in 03/2018

Workshops at Global Foundries, Samsung, Intel, IBM, Facebook

# **ODSA Workstreams**

| Workstream     | Leader          | Participants                                           | Objective                  |

|----------------|-----------------|--------------------------------------------------------|----------------------------|

| PHY Layer      | Robert Wang     | SYNOPSYS* MARVELL*                                     | PCIe PIPE adapter          |

| Bunch of Wires | Mark Kuemerle   | EXILINX SYNOPSYS ** GOOGLE SIFIVE                      | Low cost D2D PHY           |

| CDX            | Jawad Nasrullah | ZGlue ANSYS AyarLabs câdence Synopsys*                 | Chiplet design exchange    |

| Business       | Sam Fuller      | facebook  A Microsoft Azure  AyarLabs                  | Chiplet workflow           |

| PoC hardware   | JP Balachandran | facebook Achronix  Ols CO  Facebook Achronix  Achronix | PoC board design           |

| PoC software   | Kevin Drucker   | facebook Samiec MACOM. NETRONOME ZGlue                 | Application/Infra software |

| Link layer     | Open            | E XILINX (intel)                                       | ODSA Stack                 |

| Open HBI       | Kenneth Ma      | € XILINX                                               | High perf D2D PHY          |

https://www.opencompute.org/wiki/Server/ODSA

# Significant Results

- First fully open physical and logical D2D interfaces, available in 2020

- New open Bunch of Wires interface. Low development cost, very flexible

- PIPE adapter to carry PCIe/CXL over BoW PHYs

- NXP DiPort protocol to disaggregate

- Proof of concept flexible software development platform

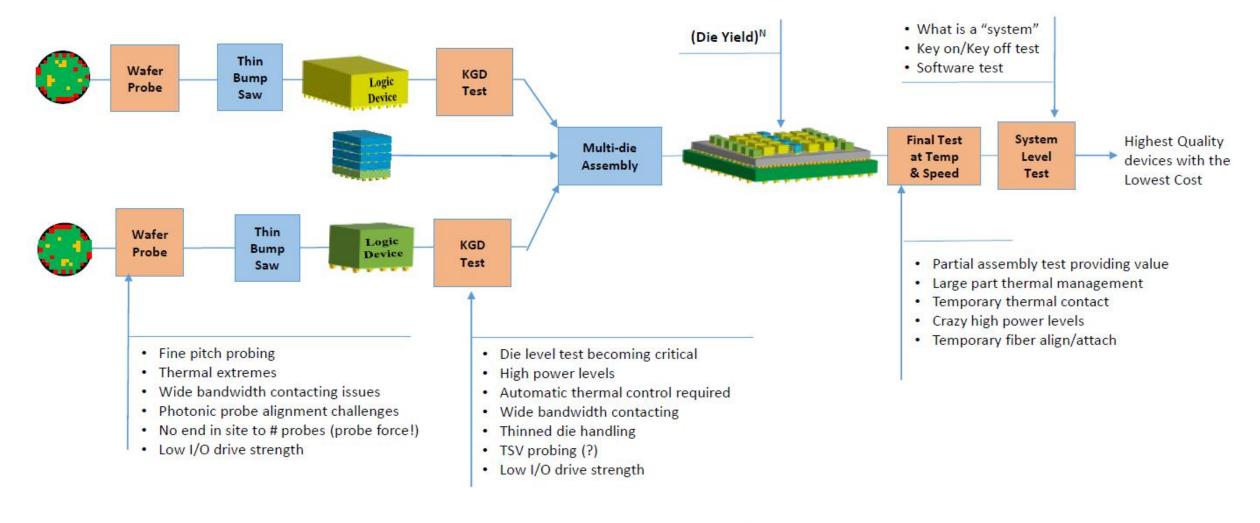

# Where we need help

- Developing the protocol stack

- Packaging and physicals

- Test

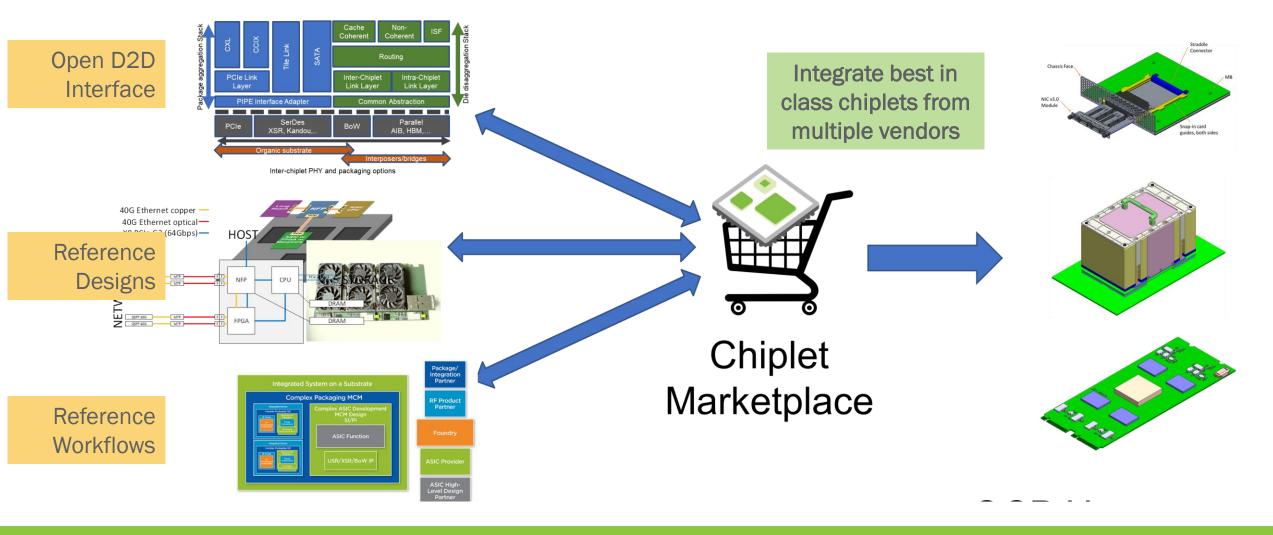

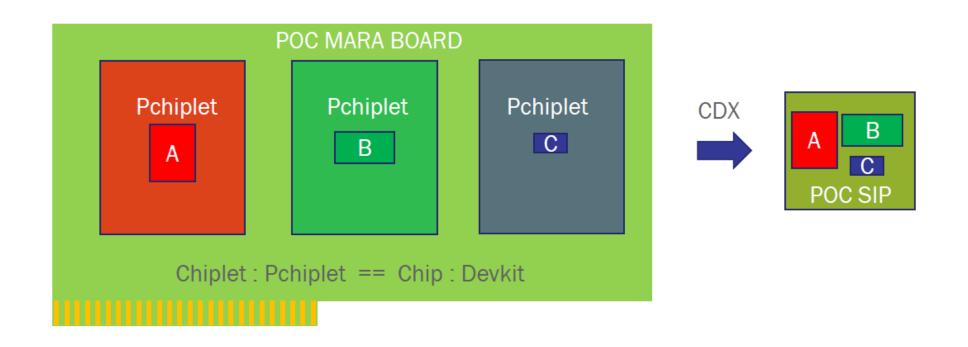

# CDX Subgroup Charter

Jawad Nasrullah, zGlue Facebook workshop, Dec. 2019

- 1- Chiplet Machine Readable Description Format Standardization

- 2- Chiplet Catalog

- 3- Pchiplet-to-SIP conversion flow

### Tomorrow (circa 2020)

Dave Amstrong, HIR Facebook workshop, Dec. 2019

## In brief...

- Open physical and logical D2D chiplet interface for best in class products

- Rapid growth, in interest, activities and results we're just getting started

- We really could use your help in packaging and test

- Join the contributors from: Achronix, AnalogX, ANSYS, ASE, Avera Semi, Ayar Labs, Broadcom, Cadence, Cisco, Facebook, Ferric, IBM, IEEE HIR, Intel, Kandou, Keysight, Lattice, Macom, Marvell, Microsoft, Netronome, NXP, On Semi, Samtec, Sarcina, Synopsys, Tamind, Xilinx, zGlue