## **ODSA:** Technical Introduction

Bapi Vinnakota, Netronome ODSA Project Workshop March 28, 2019

Consume. Collaborate. Contribute.

## **ODSA:** A New Server Subgroup (Incubation)

- Extending Moore's Law

- Domain-Specific Architectures: Programmable ASICs to accelerate high-intensity workloads (e.g. Tensorflow, Network Flow Processor, Antminer...)

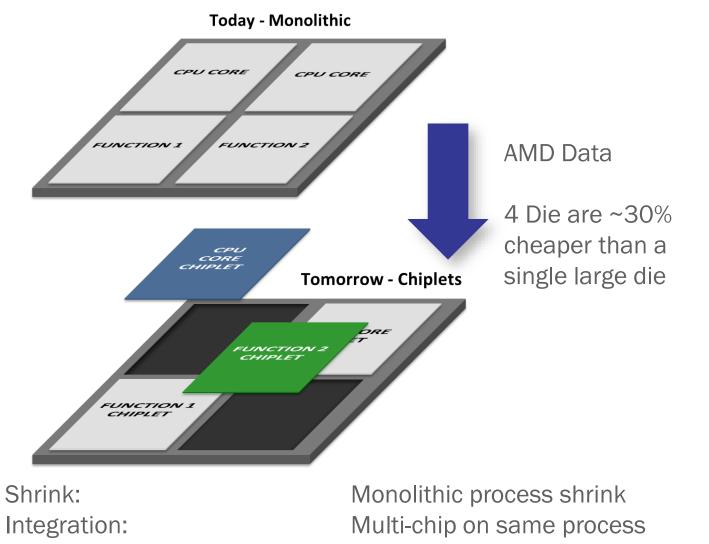

- Chiplets: Build complex ASICs from multiple die, instead of as monolithic devices, to reduce development time/costs and manufacturing costs.

- Open Domain-Specific Architecture: An architecture to build domain-specific products

- Today: All multi-chiplet products are based on proprietary interfaces

- Tomorrow: Select best-of-breed chiplets from multiple vendors

- Incubating a new group, to define a new open interface, build a PoC

- Today is our first workshop as an OCP project!

### Thanks to:

Achronix: Quinn Jacobson, Manoj Roge; Aquantia: Ramin Farjad; Avera Semi: Dan Greenberg, Mark Kuemerle, Wolfgang Sauter; Ayar Labs: Shahab Ardalan; ESNet: Yatish Kumar; Kandou: Brian Holden, Jeff McGuire; Netronome : Sujal Das, Jim Finnegan, Jennifer Mendola, Brian Sparks, Niel Viljoen; NXP: Sam Fuller; OCP: Bill Carter, Archna Haylock, Dharmesh Jani, Steve Roberts, Seth Sethapong, John Stuewe, Aaron Sullivan, Siamak Tavallaei ; Samtec: Marc Verdiell; Sarcina: Larry Zu; zGlue: Jawad Nasrullah.

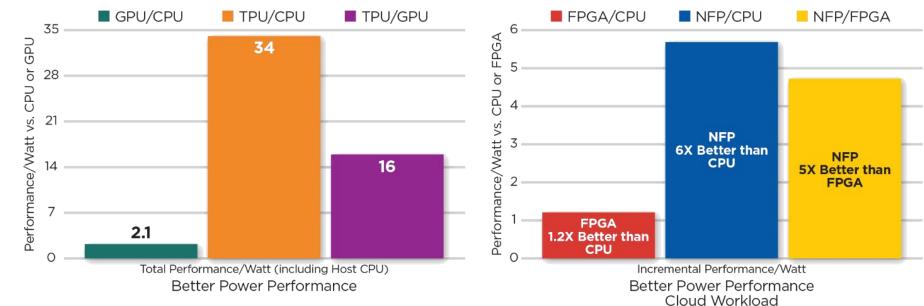

### **Domain-Specific Architectures**

### Tailor architecture to a domain\*

- Server-attached devices programmable, not hardwired

- Integrated application and deployment-aware development of devices, firmware, systems, software

- 5-10X power performance improvement

- Big more of a processor to I/O mismatch => more memory

- Each serves a smaller market

**Domain-Specific for Machine Learning and AI**

### Google TPU vs. CPU and GPU

Source: "An in-depth look at Google's first Tensor Processing Unit (TPU)," Google Cloud, May 2017

Source: Netronome, based on internal benchmarks and industry reports related to Xeon CPUs and Arria FPGA.

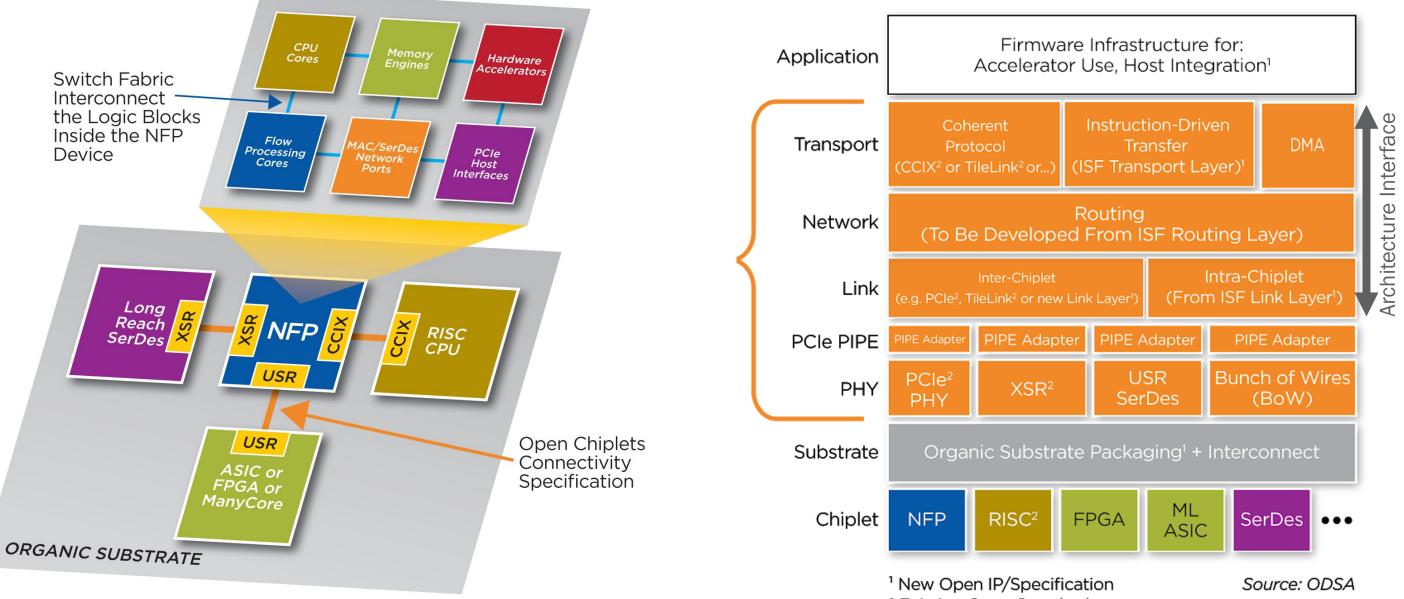

### **Domain-Specific for Networking and Security**

Cloud Workload 1 Port-blast100 | VXLAN | 1:2 Flows:Rules

Intel Xeon Gold 6138 | Intel Xeon Gold 6138P (Arria 10 GX 1150) | Netronome NFP

### Netronome NFP vs. CPU and FPGA

### Monolithic vs Chiplets

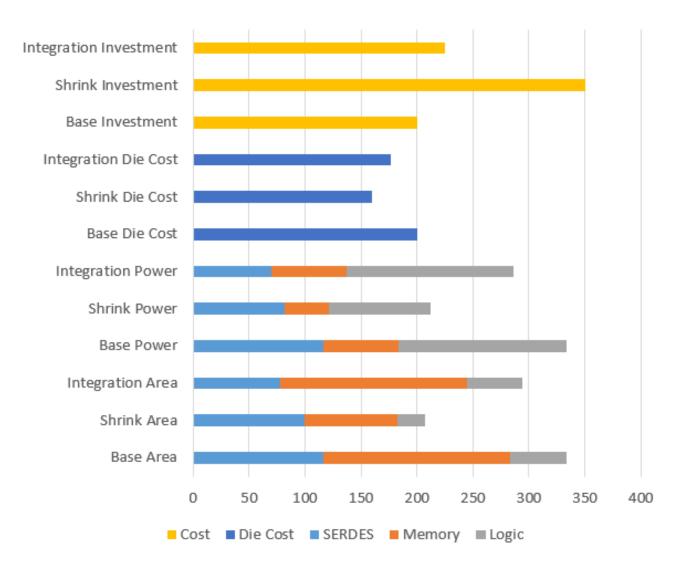

Integration provides nearly all the benefits of a shrink at a fraction of the cost, because of efficient inter-chiplet interconnect

### Area, Power and Cost for Shrink vs. Integration

https://www.netronome.com/media/documents/WP\_0DSA\_0pen\_Accelerator\_Architecture.pdf

### **COST & PERFORMANCE DISPARITY IN SCALING**

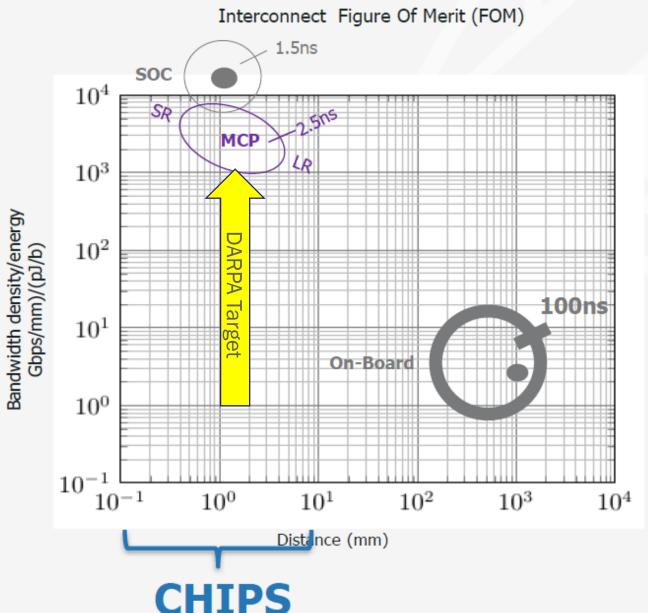

### High Density Multi Chip Packaging interconnect

- 0.1-10mm; 500IO/mm shoreline; 0.1-1.0pJ/bit

- FOM<sub>LongReach</sub>=(1Tb/mm)/(1pJ/b)=1,000

- FOM<sub>shortReach</sub>=(1Tb/mm)/(0.1pJ/bit)=10,000

- Latency=2.5ns

### **SOC-like FOM**

Distribution Statement "A" (Approved for Public Release, Distribution Unlimited)

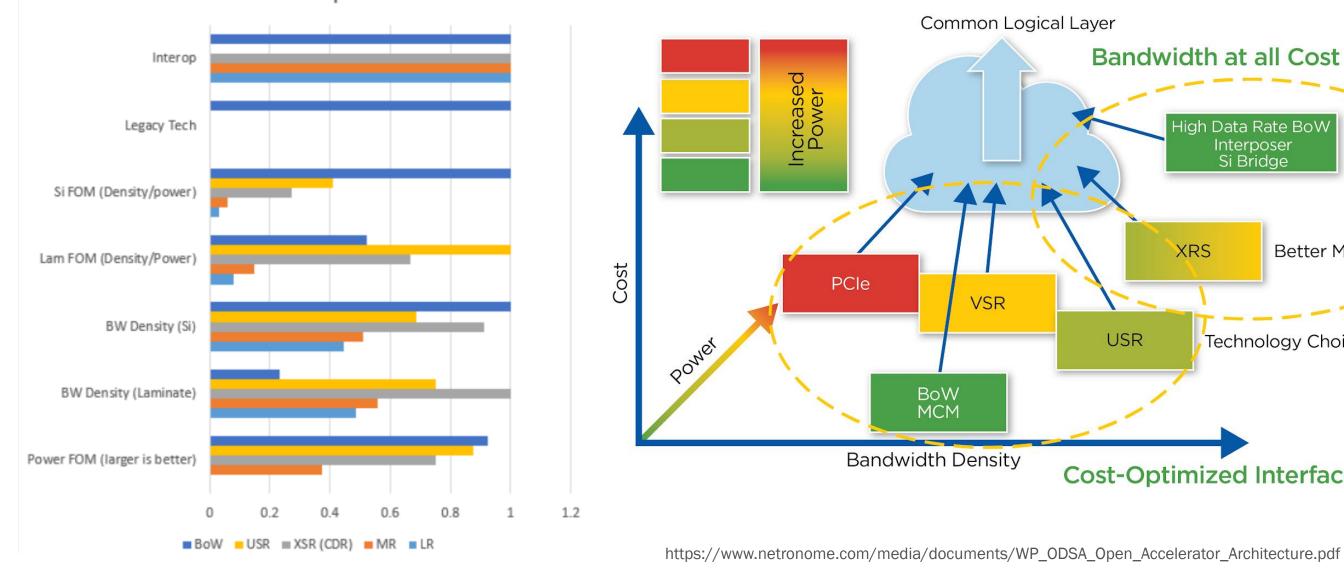

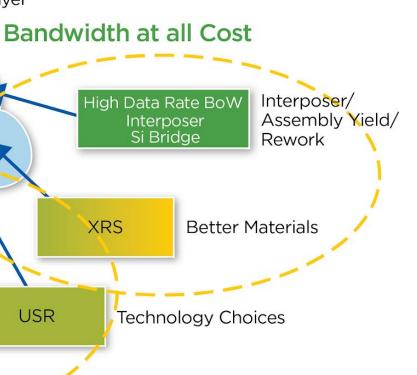

## **PHY Layer Options**

Interface Comparisons

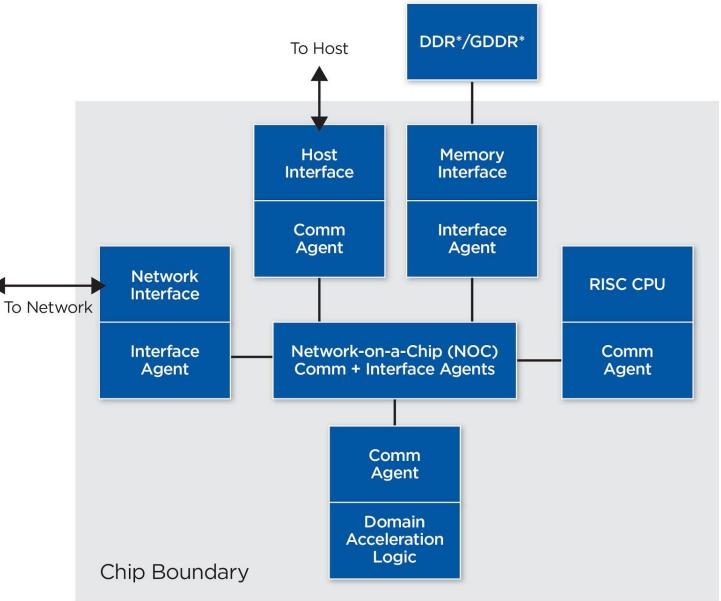

### **Domain-specific accelerators**

- Host-attached programmable logic optimized for an application domain

- Tensorflow, Netronome NFP, Crypto, IoT,...

- Domain-specific accelerators contain lots of generic logic ~35-45% of silicon area, development time

- Network, Host, Memory Interfaces

- General-purpose CPUs

- SRAM, interconnect

- Domain-specific logic works in coordination with host and/or CPU SW

- Ideally

- Investment in a DSA should be limited to the domain-acceleration logic

- In reality

- Buy IP for the "non-core" parts, spend \$\$'s test and integration

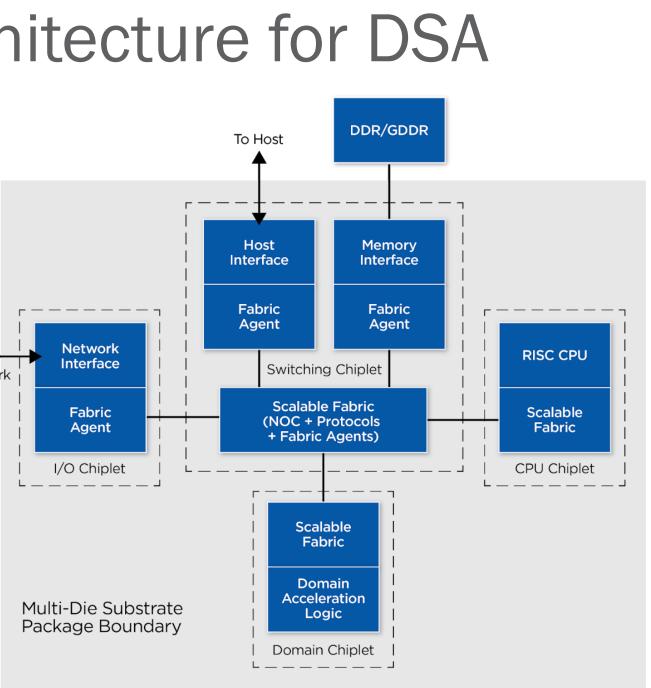

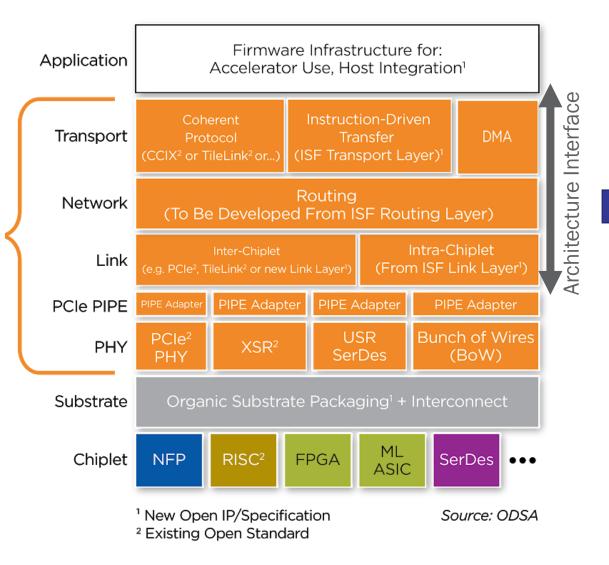

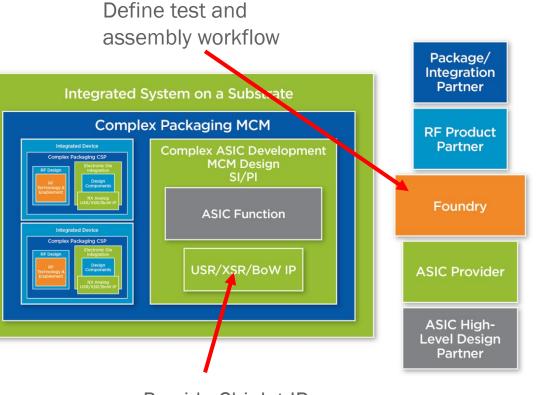

## Multi-Chiplet Reference Architecture for DSA

| <b>Design Function</b> | Value                                                                                |

|------------------------|--------------------------------------------------------------------------------------|

| IP Qualification       | Verified IP for inter-chiplet communication                                          |

| Architecture           | Leverage reference architecture.                                                     |

| Verification           | Focus investment on domain-specific logic.                                           |

| Physical               | Reuse chiplets instead of IP for 40% of the functions in a monolithic design         |

| Software               | Open source firmware and software for host-attached operation                        |

| Prototype              | Aim for reference package design with area, power budgets and pinouts for components |

| Test and Validation    | Develop workflow for chiplets                                                        |

## **Open Interface for Chiplet-Based Design**

<sup>2</sup> Existing Open Standard

Multiple chiplets need to function as though they are on one die

## Need a Scalable Interface

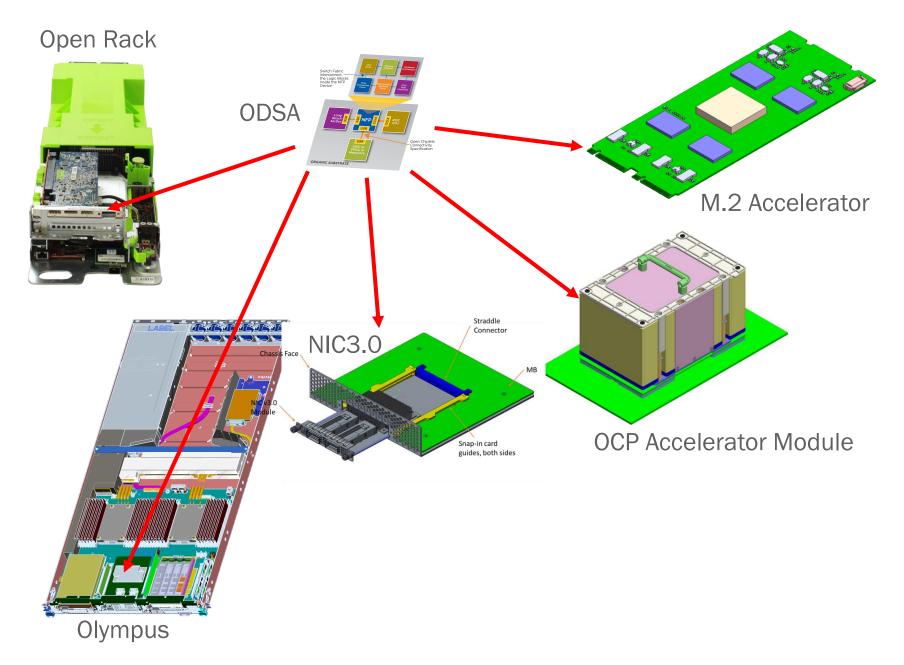

Multiple OCP projects use accelerators

Open architectural interface to multiple carrier cards

Power, management, reliability

Enable a collection of ODSAcompliant chiplets, packages, sockets, in the OCP marketplace

## requirements vary across sockets

# support accelerator designs across

## **ODSA Landing Zones**

|                 | Network I/O        | Host I/O                                                 | Power                     |  |

|-----------------|--------------------|----------------------------------------------------------|---------------------------|--|

| NIC 2.0         | Dual port x 25     | X16 PCIe Gen 3                                           | 25w                       |  |

| NIC 3.0         | Dual port x 200    | SFF: x16 PCIe Gen 4/Gen 5<br>LFF: x32 PCIe Gen 4/Gen 5   | Small: 80w<br>Large: 150w |  |

| M.2<br>M.2 Dual | N/A                | Single: x4 PCle Gen 3/Gen 4<br>Dual: x8 PCle Gen 3/Gen 4 | Single: 12w<br>Dual: 20w  |  |

| OAM             | 8x16 SerDes Lanes  | Typical: x16 PCIe                                        | 12V: 350w<br>48V: 700w    |  |

| Olympus         | Via x16 PCIe Cards | 1x16 PCIe                                                | 75W-300W PCIe AIC         |  |

| Tioga Pass      | Up to 100Gbps SH   | x32 PCIe Gen3                                            |                           |  |

Data from Ron Renwick, John Stuewe, Siamak Tavallaei, Whitney Zhao

### Small/Large

Single: 22x110 Dual: 46x110 102x165

### FHHL PCIe 6.5x20inch

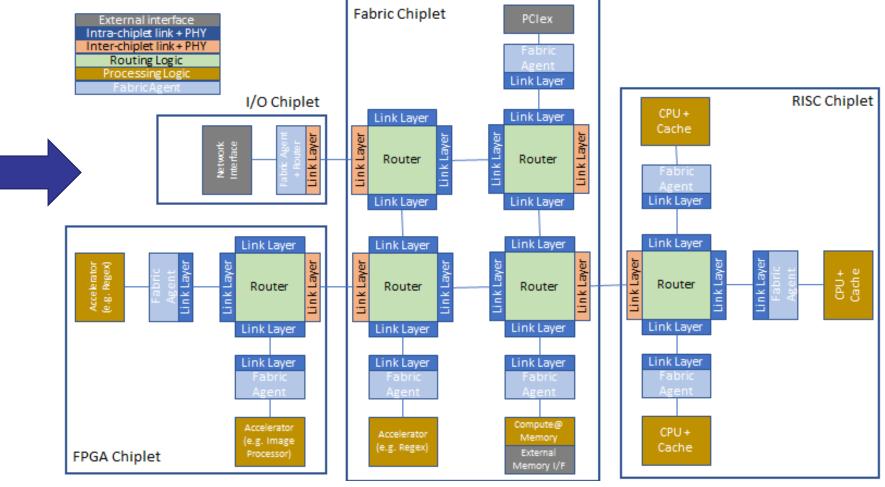

## Cross-chiplet ODSA fabric proposal

## Progress Since the Last Workshop

### • Timeline:

- ODSA Announced 10/1/18

- White Paper

- First Workshop

- Joined OCP

- Today

12/5/18 01/28/19 03/15/19 03/28/19 7 companies 10 companies 35 companies

53 companies

- PoC

- Identified components, use cases

- Standards

- Characterizing PHY, new interface proposal

- Business

- Survey, business model

## TL in the last six months

- We're solving the right problem, tbd on whether it's the right solution.

- Analog (and cache coherence) engineers have lots of opinions, likely justified, but also confusing for mere mortals.

- How you do business drives chiplet economics and your technology choices.

- Our interface definition must recognize this diversity while focusing our effort. You need a new business/workflow model that make chiplets work across this diversity

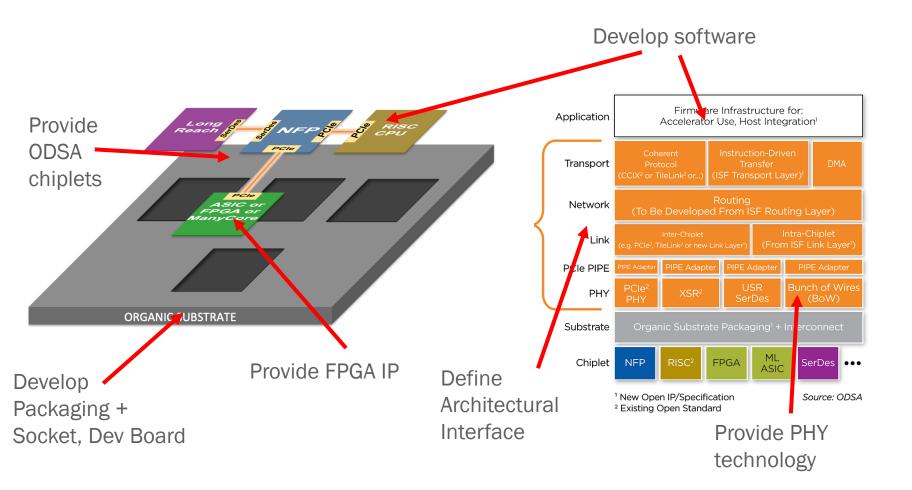

### How to Participate Please Help! : Join a Workstream

Join the PoC, Build fast: (Quinn Jacobson/Jawad Nasrullah) Join Interface/Standards: (Mark Kuemerle/Aaron Sullivan)

(Sam Fuller/Jeff McGuire)

**Provide Chiplet IP**

### Join Business, IP and workflow: