# Advanced Packaging @ IME

Institute of Microelectronics, A\*STAR, Singapore

June 2019

**CREATING GROWTH, ENHANCING LIVES**

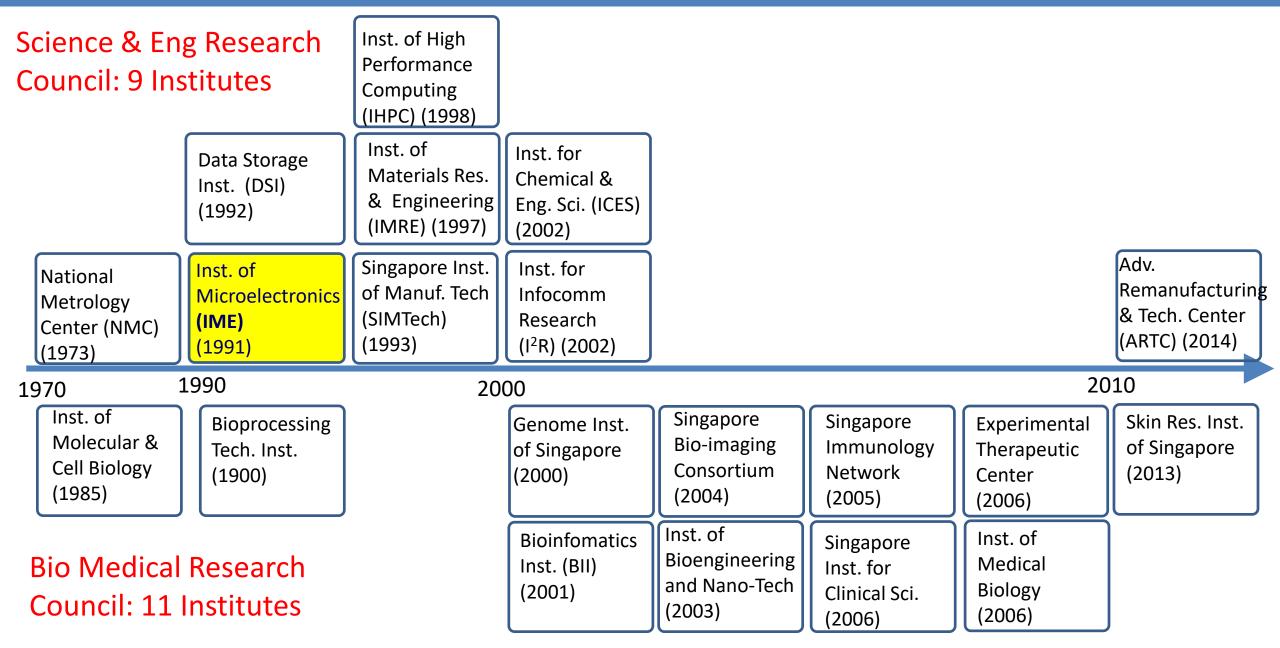

## Agency for Science Technology and Research -A\*STAR

**Mission:** Advance science and develop innovative technology to further economic growth and improve lives

| Science and<br>Engineering<br>Research Council<br>(SERC) | Biomedical<br>Research Council<br>(BMRC) | A*ccelerate<br>Technologies Pte Ltd<br>(ETPL) | A*STAR Graduate<br>Academy |

|----------------------------------------------------------|------------------------------------------|-----------------------------------------------|----------------------------|

| 9 Research Entities                                      | 11 Research Entities                     | Commercialization                             | Scholarships               |

# 4,100

Researchers, Engineers & Technical staff 38%

From 64 Countries

## **A\*STAR Research Entities**

## **Institute of Microelectronics**

### **Key Research areas**

- Advanced packaging

- Heterogeneous integration

- System in package

- Sensors and actuators

- IC Designing

- Memory enabled artificial intelligence

- Advance Optics

- Biomedical device and bio-packaging

platforms

### Infrastructure

- 12" TSV engineering line

- State-of-the equipment

- 3000m<sup>2</sup> clean rooms

- All metrology facilities

### Strategic partnerships

- Fabless, Foundries, IDM, OSAT

- Equipment, Materials makers

- Testing, EDA companies

### **Business friendly platform**

- Stringent controls and compliances

- Big pool of world class R&D talent

- Flexible collaboration models

An ISO 9001 and ISO 13485 Certified Organization

#### Science Park II

Fusionopolis

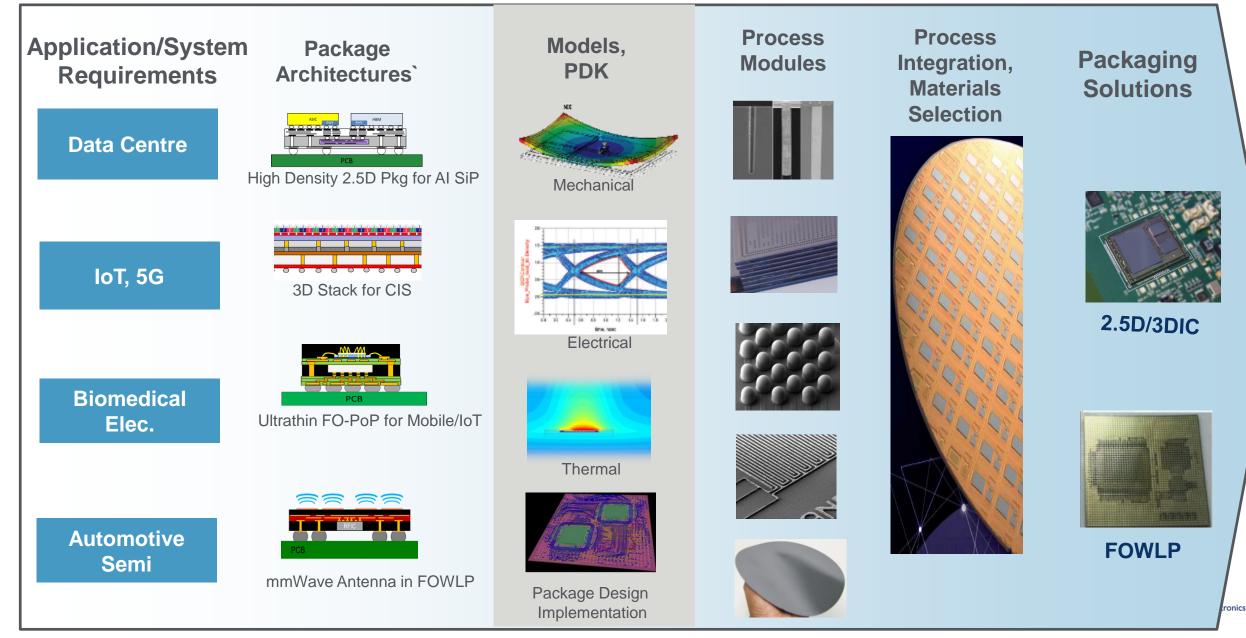

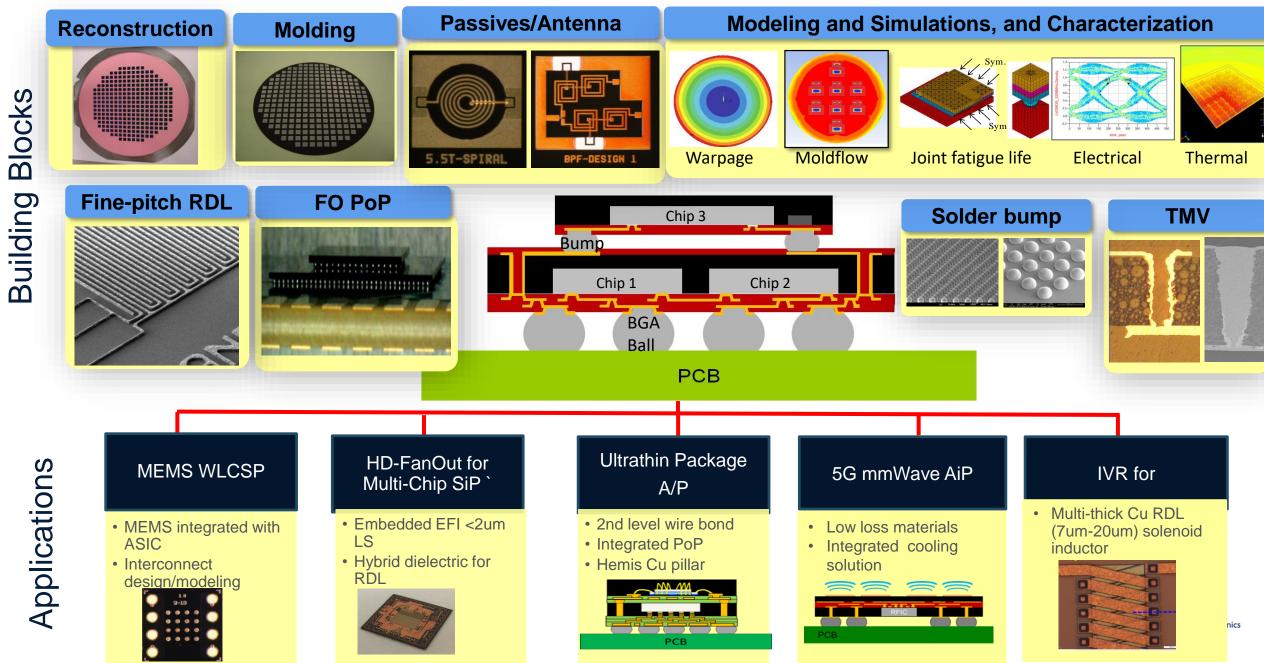

### **Advanced Package Development Approach**

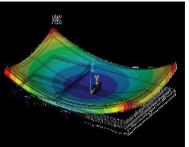

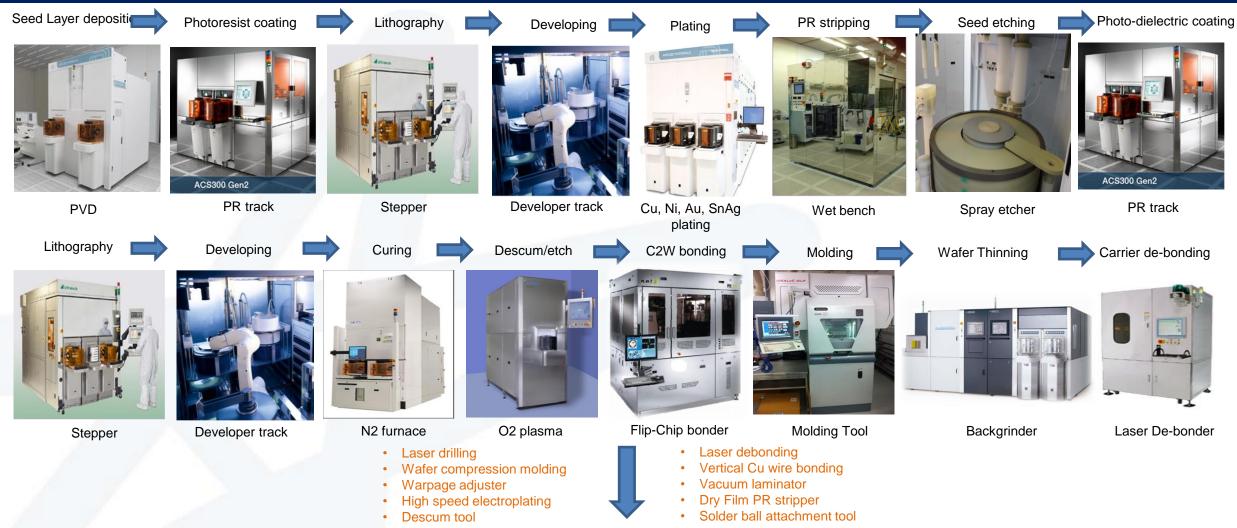

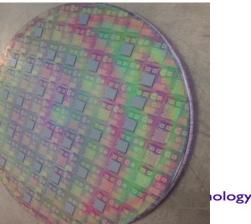

### IME's Multi-Chip Wafer Level Package Development Line

**Development of baseline FOWLP Integration for next generation applications:**

- Package-architecture, integration flow, process, tools and materials.

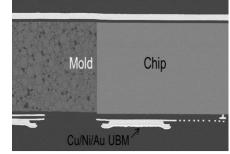

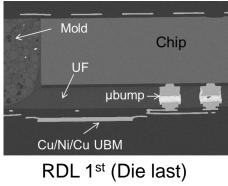

- Mold 1<sup>st</sup> and RDL 1<sup>st</sup> technologies includes TMV & TMI technologies, Multi-layer fine RDL and dielectric materials, Compression mold and moldable underfill , Thin wafer handling.

- Estimate the manufacturability, variability, reliability, cost an performance.

- Data Analytics to accelerate the cycle time for process development

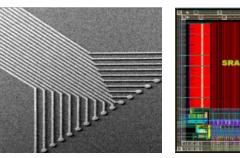

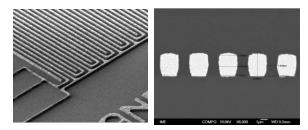

## **IME's Advanced Packaging Capabilities**

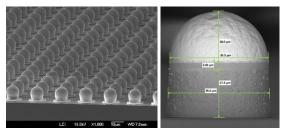

Fine Pitch RDL L/S of 2µm

Micro-Via of up to 2µm in polymer dielectric for fine pitch RDL

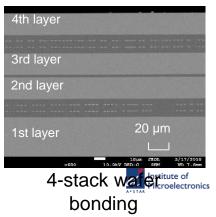

Multi-Layer RDL up to 4 layers

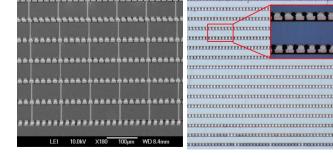

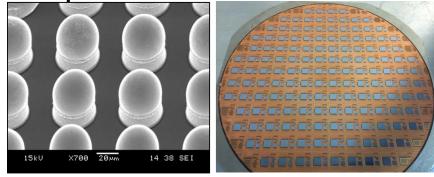

Fine pitch Cu Pillar bumping up to 20µm pitch

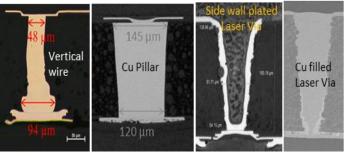

Through Mold Interconnections for FO PoP

TSV with BEOL RDL TFI with BEOL-RDL for TSV interposer L/S of 0.4µm

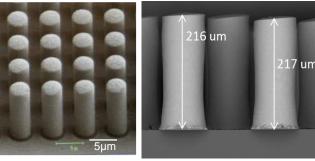

Cu Pillar bumping: Fine pitch up to 6µm pitch & tall pillar of >200µm height

Mold 1<sup>st</sup> (Die 1<sup>st</sup>) FOWLP with L/S of 5µm

FOWLP with L/S of 2µm

3D Chip Stacking (up to 15 dies) using 20µm pitch interconnections

C2W 6µm pitch Cu-Cu bonding

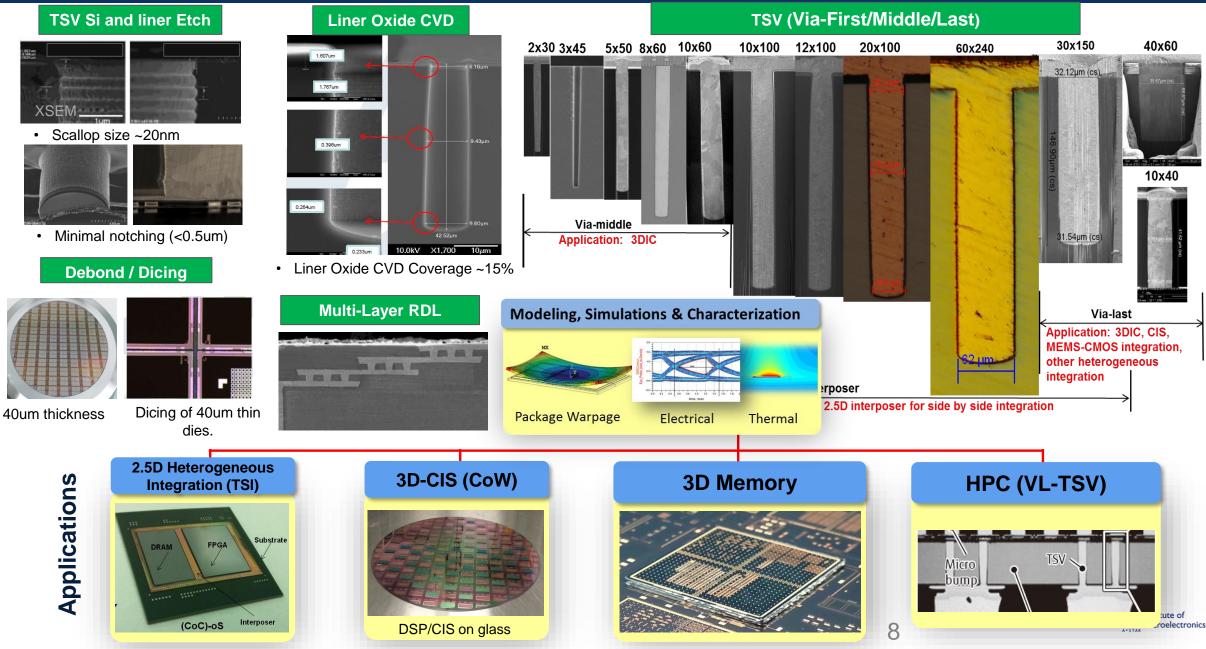

## 2.5D/3DIC Platform

Blocks

Building

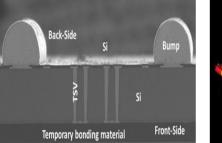

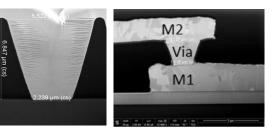

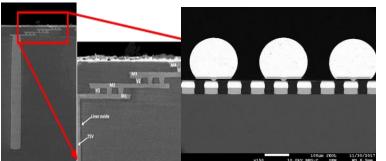

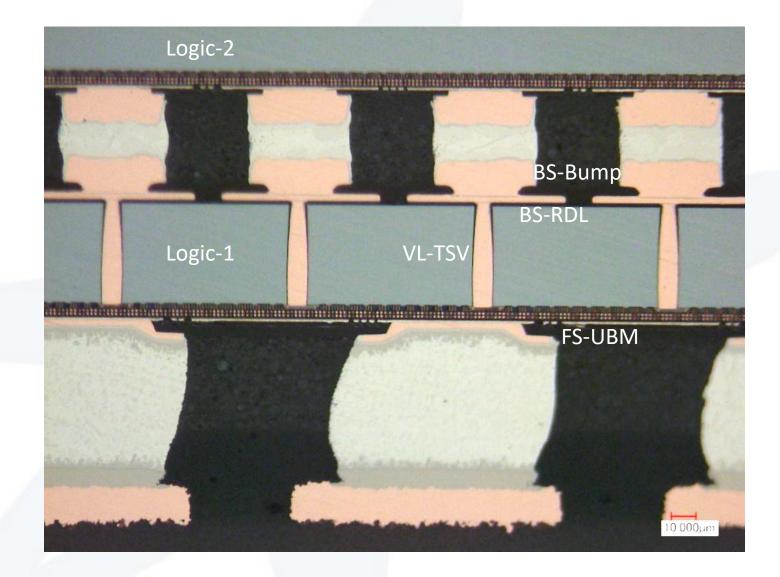

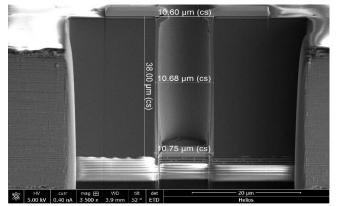

## Via-Last from Backside Demonstration for HPC Application

- IME demonstrated FS-UBM, VL-TSV, BS-RDL and BS SnAg/Cu-pillar capabilities on CMOS Logic device wafers.

- 10 x 40um VL-TSV was successfully demonstrated.

- ✓ Good overlay control (back-to-front mis-alignment <1um)</li>

- ✓ Good TSV etch profile (no notching)

- ✓ Good liner coverage (sidewall oxide thickness >200nm)

- ✓ Good connectivity with M1 (no under/over etching)

- ✓ Good TSV Cu filling (no void)

- ✓ Good bump height uniformity control (non-uniformity<5%)</li>

Agency for Science, Technology and Research

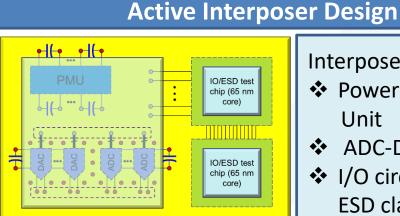

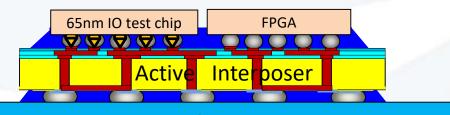

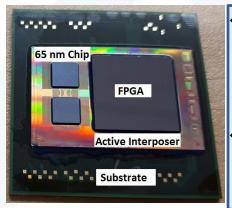

## **Heterogeneous Integration on Active Silicon Interposer**

### Interposer functions

- Power management Unit

- ✤ ADC-DAC

- ✤ I/O circuits including ESD clamps, De-Caps

### **Active Interposer Package Schematic**

#### Substrate

- Heterogeneous Integration of \* 28nm node FPGA, 65 nm I/O chip and 130 nm ATSI demonstrated

- •••• Assembly capability involving 40µm thickness and 25mmx35mm Interposer.

### **Highlights**

- Demonstrated Active Si Interposer platform (via last fabrication, assembly & packaging

- Active Interposer function to validate

- 1. IO ESD partitioning

- 2. System scaling benefits with ADC-DAC and PMU in ATSI

- 3. System cost reduction

### **Via Last TSV Fabrication and Assembly**

- \* 40 μm ATSI functional wafers (AR: 1:4) fabricated via-last from Backside.

- Chip to Wafer bonding of FPGA and I/O Chip.

ING GROWTH. ENHANCING

## Fan-Out Wafer Level Packaging (FOWLP) Platform

## High Density RDL 1<sup>st</sup> FOWLP for Multi-Chip Packaging

|                   | Si Si chip<br>without distortion |                        | RDF and small via opening (3um)             | in<br>Vertical Wire Interconne                   |

|-------------------|----------------------------------|------------------------|---------------------------------------------|--------------------------------------------------|

|                   | Meander                          | Leakage<br>Current (A) | short via                                   | for TMI                                          |

| Wafer<br>location | 2 um                             | @0-5 V                 | <b>E</b> <sup>0.12</sup>                    | Thick PR pat <u>ter</u> ning for C<br>pillar TMI |

| center            | 2.01                             | 3.56E-13               | <b>D</b> 0.06                               | -center                                          |

| left              | 2.01                             | 3.71E-13               | <b>J</b> 0.04                               | -down<br>-left tasym                             |

| right             | 2.02                             | 3.78E-13               | 0                                           |                                                  |

| top               | 2.15                             | 3.06E-13               | 615 2 2 2 2 2 3 3 3 3 7 7 7 7 7 7 7 7 7 7 7 |                                                  |

| bottom            | 2.20                             | 3.34E-13               | Voltage (V)                                 |                                                  |

| Average           | 2.07                             | 3.49E-13               |                                             | 812                                              |

Meander structure: Average leakage current: ~3.5x10-13 Amp @ 5V

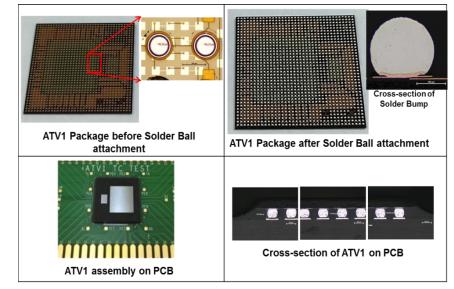

#### Fine Pitch RDL (L/S:2um/2um) & TMI for PoP

Multi-chip FOWLP (20 x 20 mm<sup>2</sup>) with ~2400 I/Os

#### Multi-chip FOWLP of 15 x 15 mm<sup>2</sup> with 1367 I/Os

|                                       | Test condition | Sample size | Results                     |

|---------------------------------------|----------------|-------------|-----------------------------|

| 15 x 15 mm <sup>2</sup><br>size FOWLP | MSL 1          | 10          | Passed (10/10)              |

|                                       | MSL 3          | 10          | Passed (10/10)              |

|                                       | TC             | 10          | Passed 500 cyc (10/10)      |

|                                       | ТСоВ           | 10          | Passed first TC 100 (10/10) |

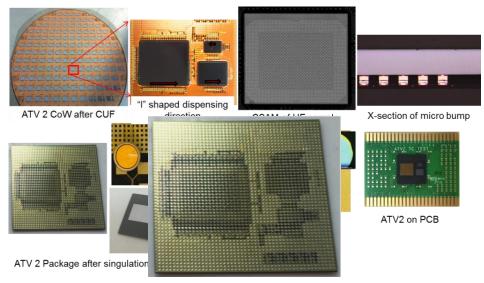

Micro bumping, C2W and Reliability Data Croelectronics

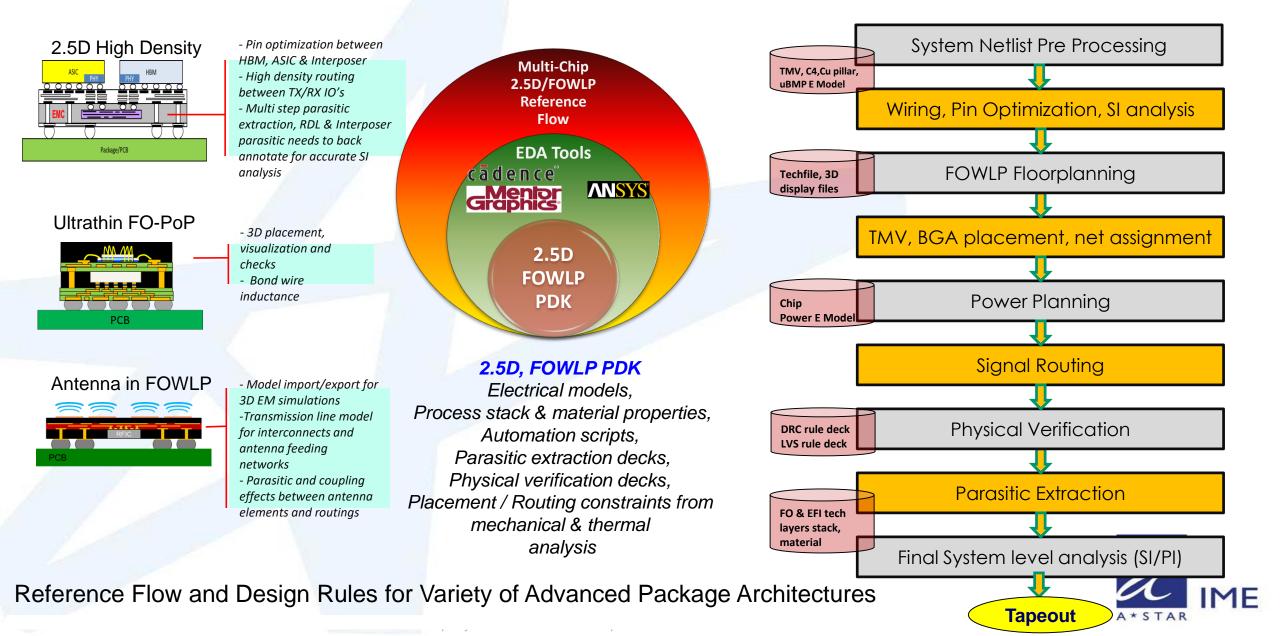

## Multi-Chip High Density Fan-Out Packaging Applications

| High Density FOWLP<br>For GPU + HBM |  |  |  |  |

|-------------------------------------|--|--|--|--|

|                                     |  |  |  |  |

#### Ultra-Thin FO-PoP for Mobile

mmWave Antenna in Package for 5G

### **Specifications**

- Package I/O count: ~2000

- Min. EFI L/S 0.4um/0.4um, 3-4 layers

Package/PCB

- Package size: >30mm x 25mm

- Chip size: 21mm x 17mm, 5mm x 7mm

### **Specifications**

- Package I/O count: ~1200

- RDL L/S 2um/2um, 2 layer

- Package size: ~15mm x 15mm

- AP size: ~11mm x 11mm

- TMV scaling <300um; Total PoP ~ 0.8mm

- Integrated Thermal Solution

### Specifications\*

- Package I/O count: 100-200

- RDL L/S: 5um/5um, 2-3 layers

- Package size ~ 10mm x 10mm

- No of chips: up to 4

- Array antenna

## Multi-Chip 2.5D/FOWLP PDK and EDA Reference Flow

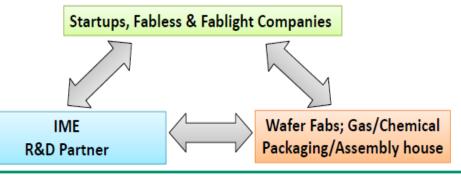

### **IME's Advanced Packaging Business Model**

- IME offers Capabilities and Technology Platforms in 2.5D/3DIC, WLP (300mm and 200mm)

- Developing transferable, production-worthy 2.5D, 3DIC, WLP solutions utilizing heterogeneous integration.

- Demonstrating prototypes for integration into system-boards and products.

- Critical Mass for Impactful Cost-effective R&D Partnership

- Small scale pilot runs to enable customers to bring products to markets quickly

- Support Multiple-Party Collaborative Model

- Bridge gaps between Chip Company, Foundry, Substrate-manufacturer, SAT, Equipment manufacturer to allow for technology to ramp into production.

# THANK YOU