## Optics in Future AI Systems: Interconnects, Switching and Processing

#### **Open Compute Project**

Panel Discussion at OFC

Tuesday, 07 March, 10:45 – 11:45

Theater II

Project

#### Optics for Future Al Systems: Interconnects, Switching and Processing

CEO LightCounting

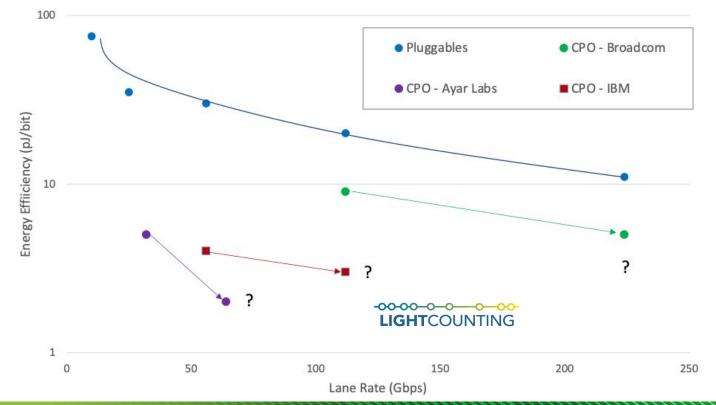

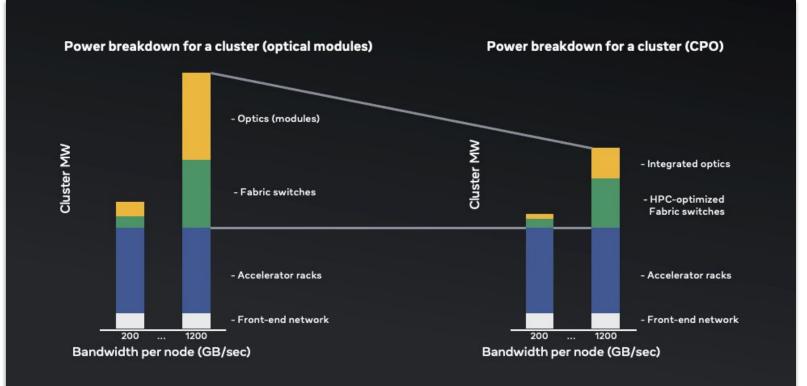

### **Progress in reducing power consumption**

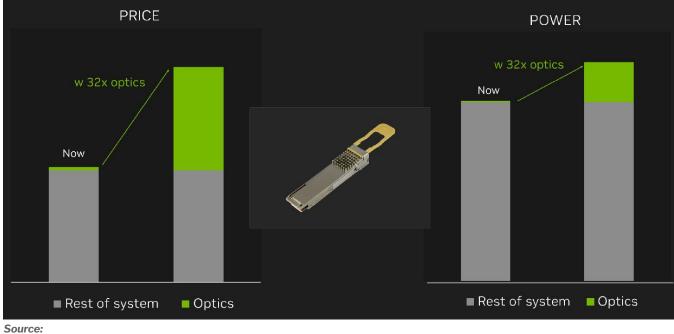

#### NVIDIA needs 32x more bandwidth now

NVidia

### Beyond CPO: 1pJ/bit and >1Tbps/mm

100 mm

Source: Nvidia, Beyond CPO: A Motivation and Approach for Bringing Optics Onto the Silicon Interposer, published Feb 15, 2023

# **Thank You**

Home

# Uday Poosarla

Technical Sourcing Manager, Optical Interconnects, Meta

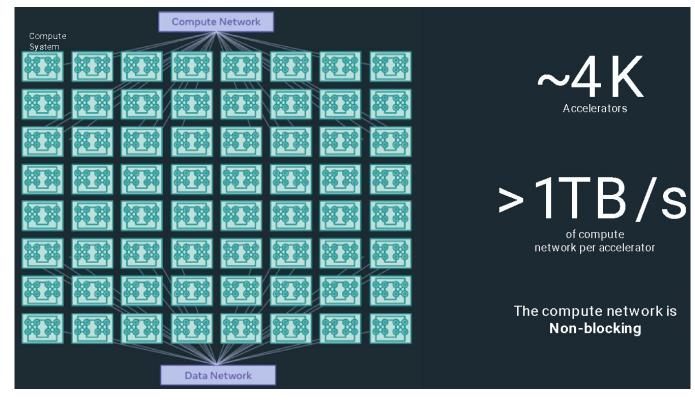

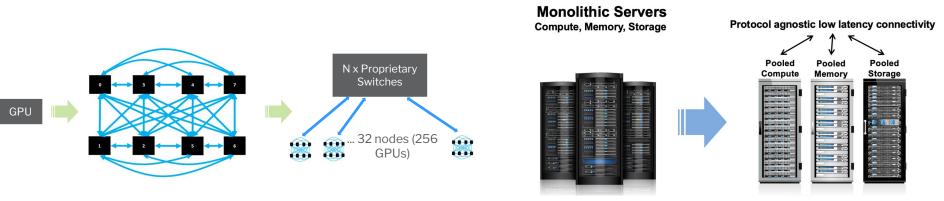

### AI Training Cluster of the Future (2025+)

Community-driven hyperscale innovation for all.

Source: Meta

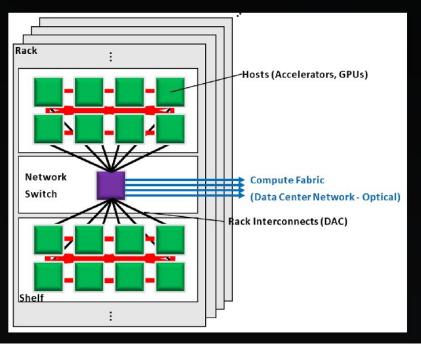

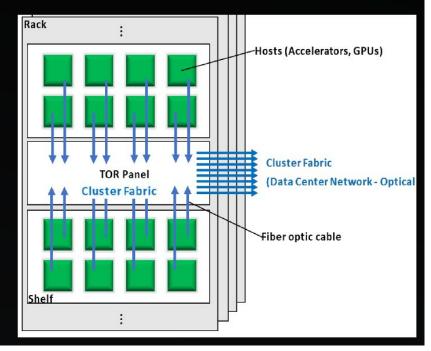

### **Interconnect Scaling Challenges**

#### Compute Fabric Today

#### **Cluster Fabric Tomorrow**

#### Source: Meta

#### **Optical I/O**

#### **Integration has Power Advantage**

Source: Meta

# **Thank You**

Home

# Andreas Bechtolsheim

OCP Board, Co-Founder and Chairman Arista

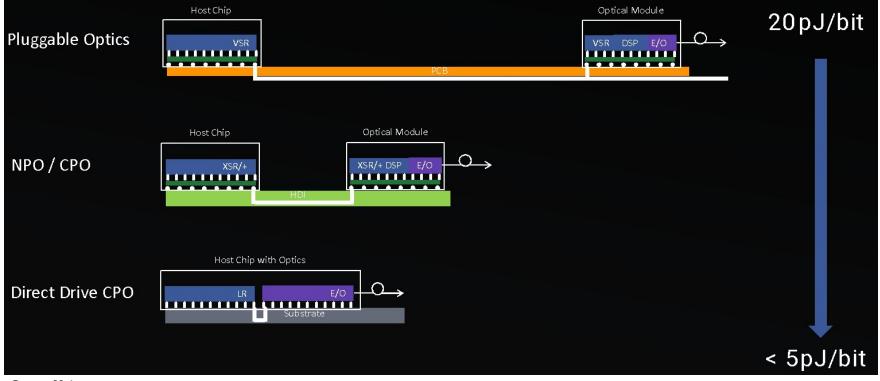

### **Linear Drive Optics Modules**

- **1. Linear Drive means no DSP or CDR** Just a linear driver to provide required modulator voltage

- **2. Requires a high-performance switch SERDES** And very careful signal integrity design

- **3. Achieves power savings similar to direct drive CPO** While retaining the many advantages of pluggable optics modules

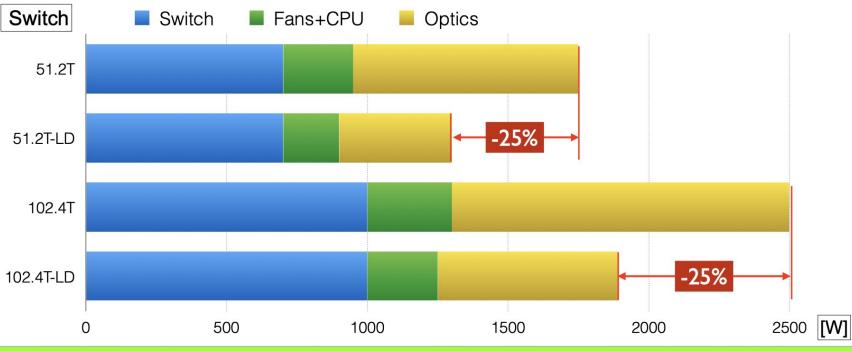

Opportunity to cut optics module power by 50% and system power by up to 25%

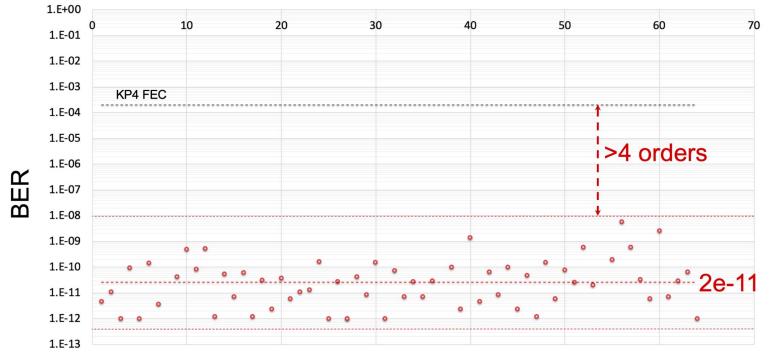

#### Pre-FEC BER with Ethernet Traffic Port #

Measurements with Silicon Photonics

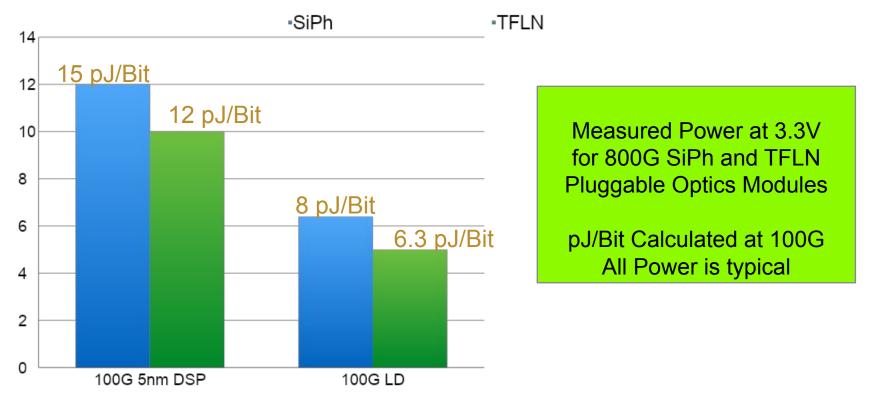

#### **800G LD Pluggables Power Evolution**

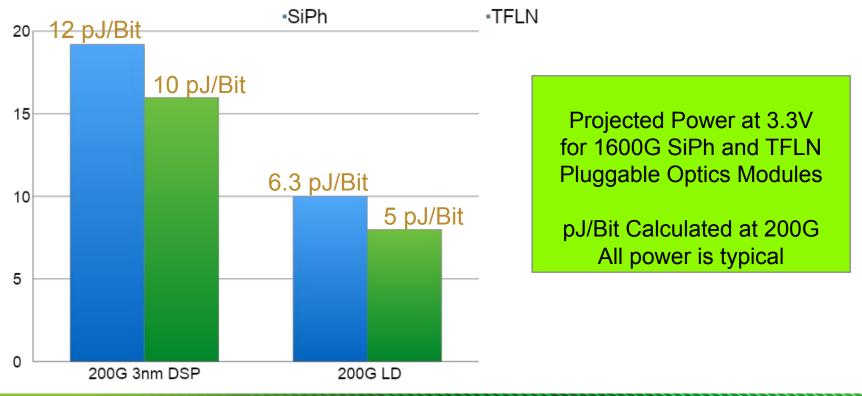

### **1600G LD Pluggables Power Evolution**

### System Level Power Savings with LD Optics

#### Additional power savings possible with non SiPh Modulators

## EOM Technology Comparison for 200G

| Technology           | Integration<br>Capability | Bandwidth  | Vpi (1) | Insertion Loss<br>(2) | Reliability  | HVM (3)  |

|----------------------|---------------------------|------------|---------|-----------------------|--------------|----------|

| Silicon<br>Photonics | Excellent                 | Sufficient | High    | High                  | Proven       | Now      |

| III-V                | Low                       | Higher     | Low     | Low                   | Proven       | Now      |

| TFLN                 | Low                       | Very High  | Low     | Low                   | Proven       | 2024 (E) |

| вто                  | New Process               | Very High  | Low     | Low                   | Proven       | 2025 (E) |

| Organic              | New Process               | Very High  | Low     | Low                   | To be Proven | 2026 (E) |

- (1) Lower Vpi lowers driver power consumption

- (2) Lower insertion loss lowers laser power

- (3) HVM = High volume manufacturing

### LPO Comparison to Direct Drive CPO at 200G $\lambda$

| Form Factor     | LPO                              | СРО                               | CPO Delta          |  |

|-----------------|----------------------------------|-----------------------------------|--------------------|--|

| DSP             | N/A                              | N/A                               | Same               |  |

| Linear Driver   | Required                         | N/A                               | Lower Power        |  |

| External Laser  | N/A                              | Required                          | Higher Power       |  |

| New EOM Tech    | Supported                        | Not POR                           | Higher Power       |  |

| Voltage Rail    | 3.3V                             | Device Voltage                    | Adjust for voltage |  |

| Projected Power | 6.3 pJ/Bit SiPh<br>5 pJ/Bit TFLN | 5 pJ/Bit SiPh @<br>Device Voltage | Very similar       |  |

### Laser Efficiency at Temperature

- **1. Laser efficiency at high temperature is key** Laser temperature inside modules can reach 75C - 85C

- **2. Desirable to avoid Thermo-Electric Coolers** TECs significantly reduce net laser power efficiency

- **3. QD Lasers offer highest efficiency at temp without TEC** Also offer fundamentally better reliability than QW lasers QD lasers achieve additional power savings at high temperature. These savings apply to any optics implementation (DSP, LD, CPO)

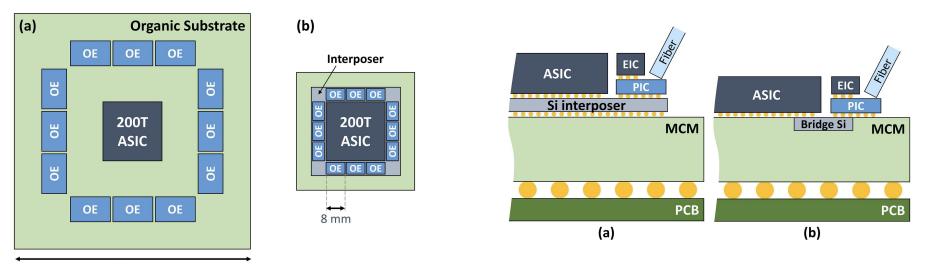

### Silicon Interposer Optics ("Beyond CPO")

- **1. Ultra low-power silicon interposer electrical interface** This lowers electrical signaling power beyond today's CPO

- **2. Potential electrical power savings vs LR: 2 pJ/Bit** About 10% compared to 102.4T switch baseline with DSP optics

- **3. Requires a very special low-power high-speed SERDES** Which cannot drive anything else except this interface

### **Adding Up The Switch Power Savings**

Pluggable SiPh LD optics modules can achieve **25% power savings**

Pluggable best in class LD optics can achieve 3**0% power savings**

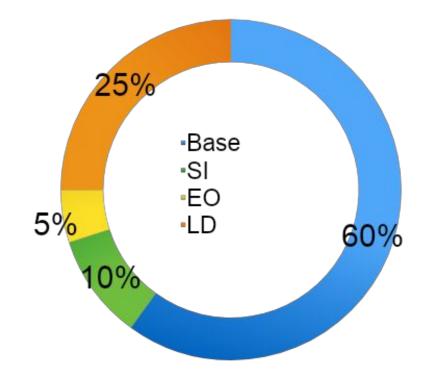

25% Linear-Drive (no DSP)5% Energy efficient modulators10% Silicon interposer interface60% Rest of switch power

# **Thank You**

Home

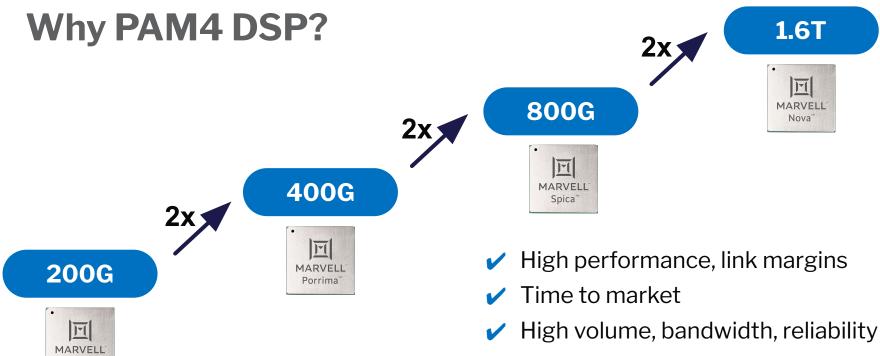

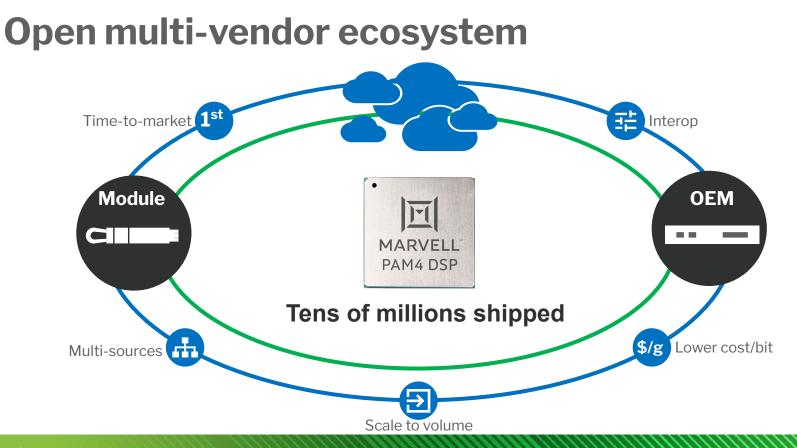

EVP/GM, Optical and Copper Connectivity Group Marvell

#### What data center operators want

Polaris"

D P E N

- Lower power / cost per bit

- Open multi-vendor ecosystem

# **Thank You**

Home

# Hamid Arabzadeh

Chairman and CEO, Ranovus

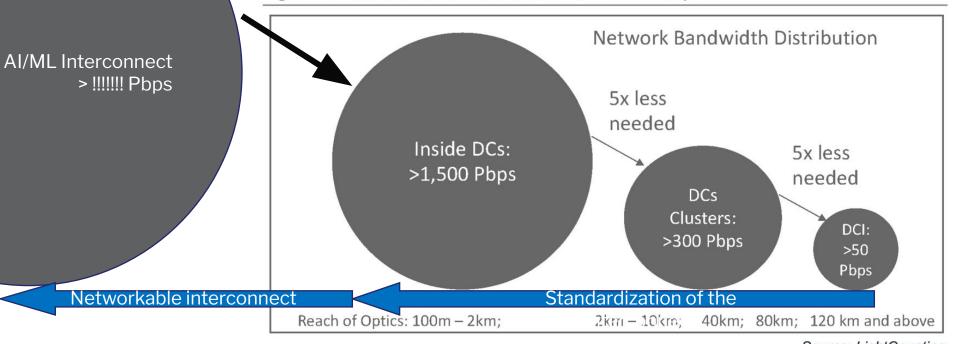

Figure 1-3: Bandwidth distribution in networks of Cloud companies

Source: LightCounting

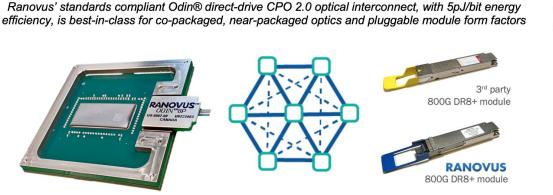

#### Al accelerator + direct drive 800G CPO interworking **RANOVUS** with retimed 800G standards-based Ethernet module

AMD Versal ACAP co-packaged with Ranovus' Odin® direct-drive CPO 2.0 3<sup>rd</sup> party 800Gbps DR8+ pluggable module and Ranovus 800Gbps DR8+ pluggable module

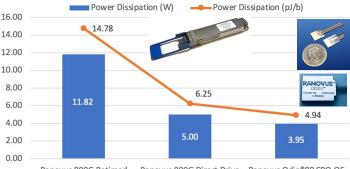

Ranovus 800G Retimed Ranovus 800G Direct Drive Ranovus Odin®8P CPO OE Pluggable Pluggable

| Device                         | Power<br>Dissipation<br>(W) | Power<br>Dissipation<br>(pJ/b) | % of Power<br>Dissipation |

|--------------------------------|-----------------------------|--------------------------------|---------------------------|

| 800G Odin <sup>®</sup> 8P EPIC | 2.75                        |                                |                           |

| Integrated Lasers              | 1.20                        |                                |                           |

| 800G Odin®8P OE + ILS          | 3.95                        | 4.94                           | 33%                       |

| 800G PAM4 IC                   | 6.4                         | 8.00                           | 54%                       |

| Pwr Conv. + Misc               | 1.47                        | 1.84                           | 12%                       |

| OSFP Module                    | 11.82                       | 14.78                          | 100%                      |

#### All power values are Typical measured numbers

Odin®8P CPO power consumption does not include microcontroller and power conversion

Do AI systems need **retimed** standardized I/O to scale?

GPU scale-out for AI training workloads

#### Disaggregated Memory for Al inference workloads

RANOVUS

#### Standardized Ser/Des + Direct Drive optical I/O hold a promising future for AI systems interconnect

# **Thank You**

Home