# **Motivation for ODSA** & Fit into OCP

Dharmesh Jani (DJ) OCP Co-chair and Open Ecosystem Lead Facebook

## **Open.** Together.

**ODSA**

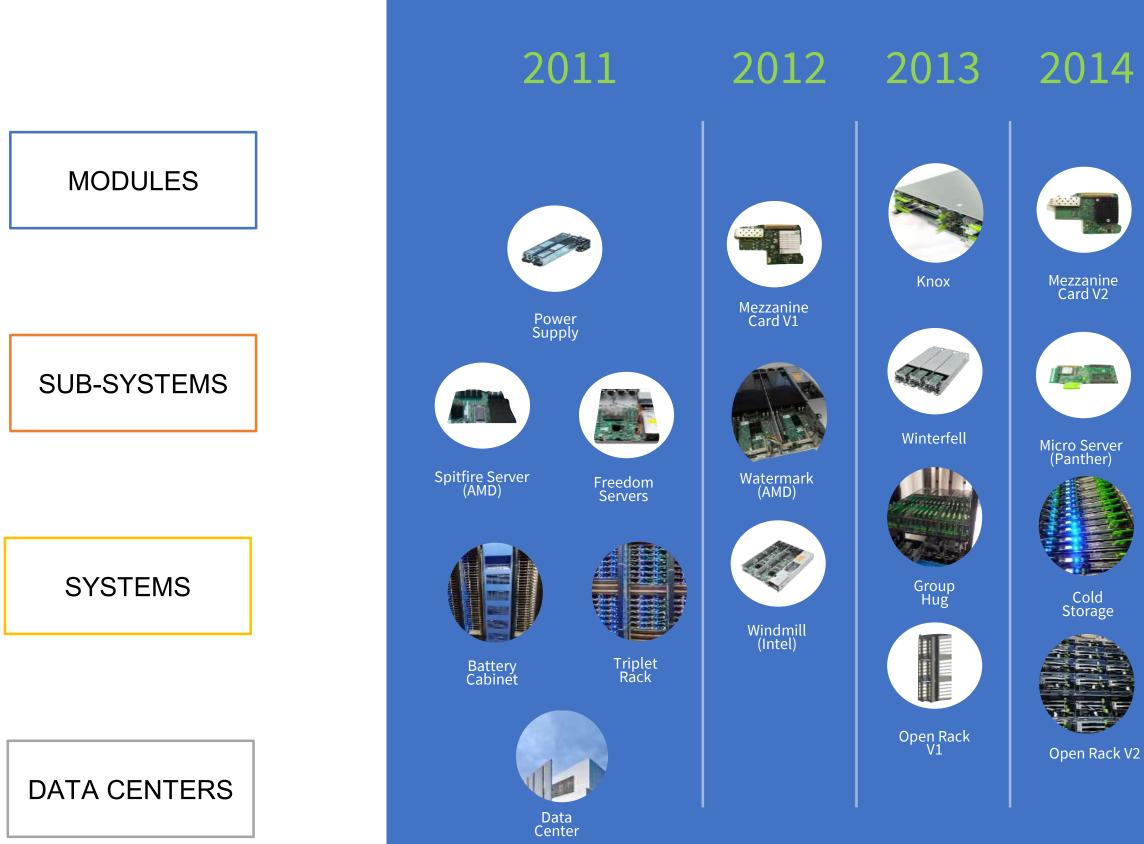

# OCP continues to evolve and grow

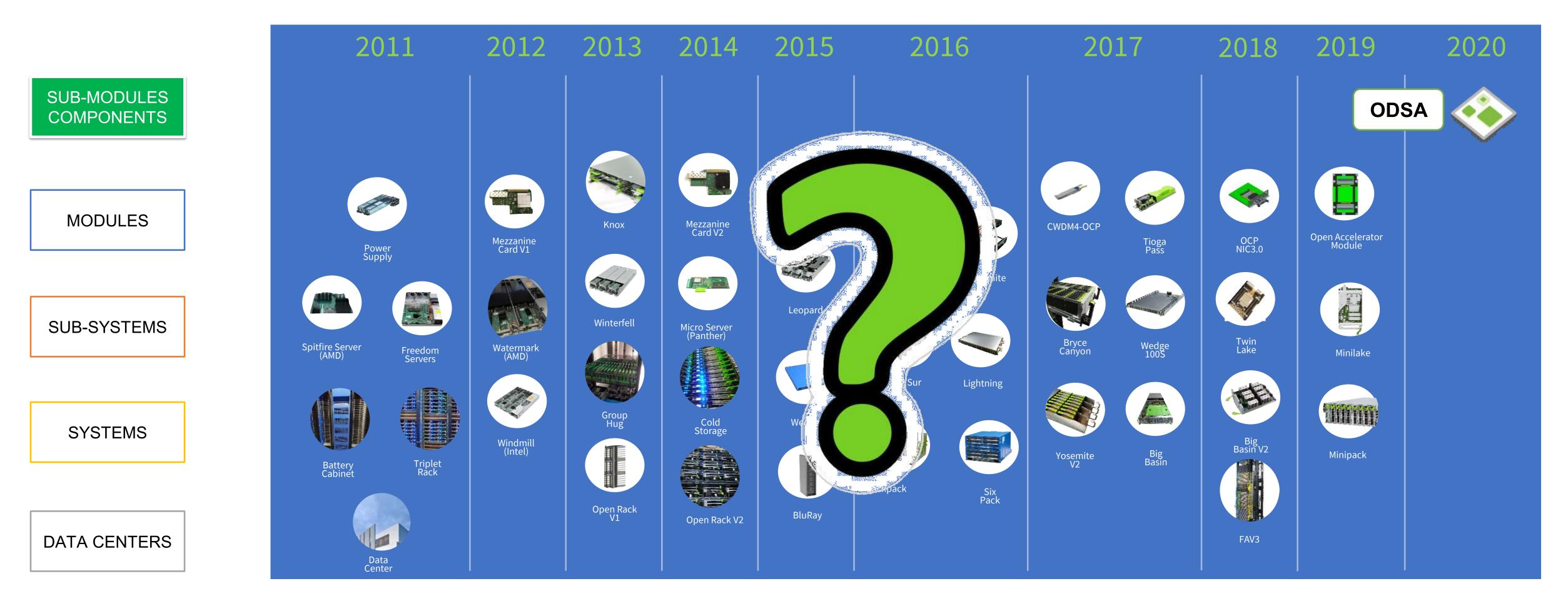

2016 2015 2017 2019 2018 OCP **Accelerator** Module Open Accelerator Module CWDM4-OCP OCP NIC3.0 Tioga Pass Leopard Minilake Bryce Canyon Twin Lake Wedge 100S Lightning File Minipack Big Basin V2 Big Basin Yosemite V2 Six Pack BluRay FAV3

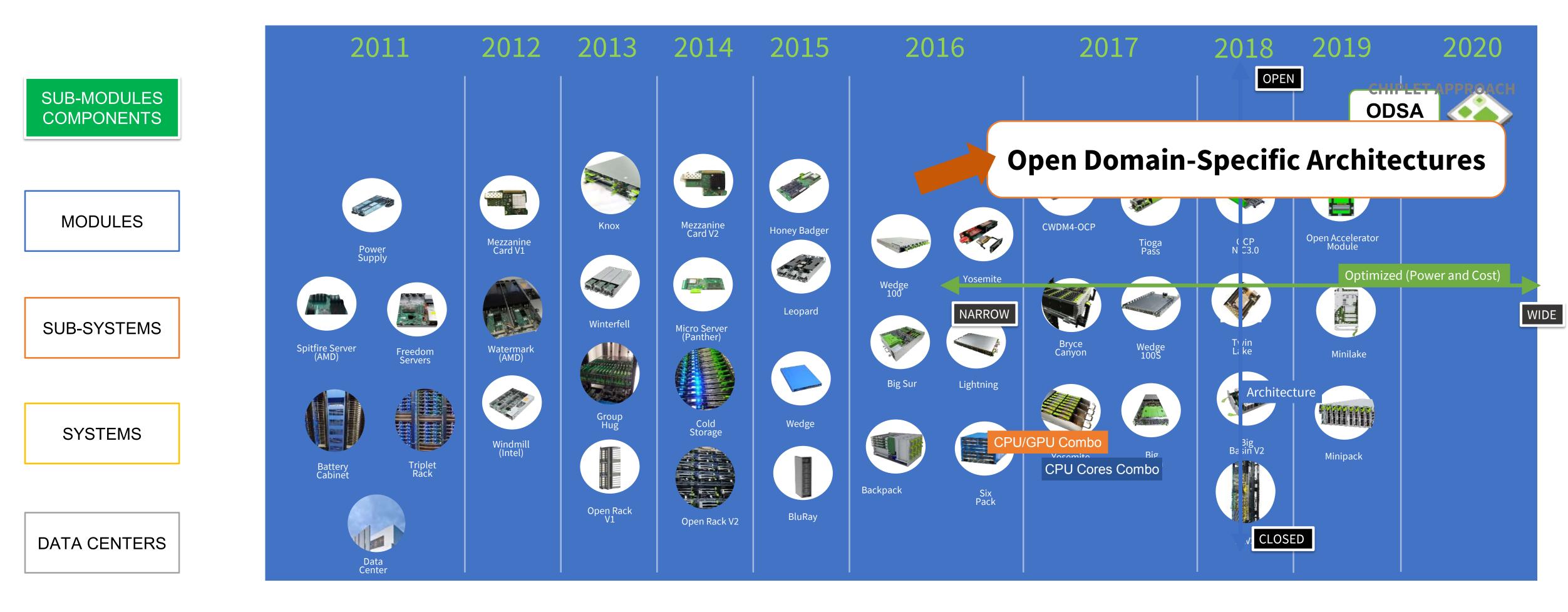

# **Open Domain-Specific Architecture (ODSA)**

#### **CHIPLET APPROACH**

CPU/GPU Combo

**CPU** Cores Combo

#### **Open Domain-Specific Architectures**

Optimized (Cost and Power)

Architecture

## Open. Together.

WIDE

# ODSA: Natural Next Step for OCP

# **ODSA: Natural Next Step for OCP**

# Start at the beginning...

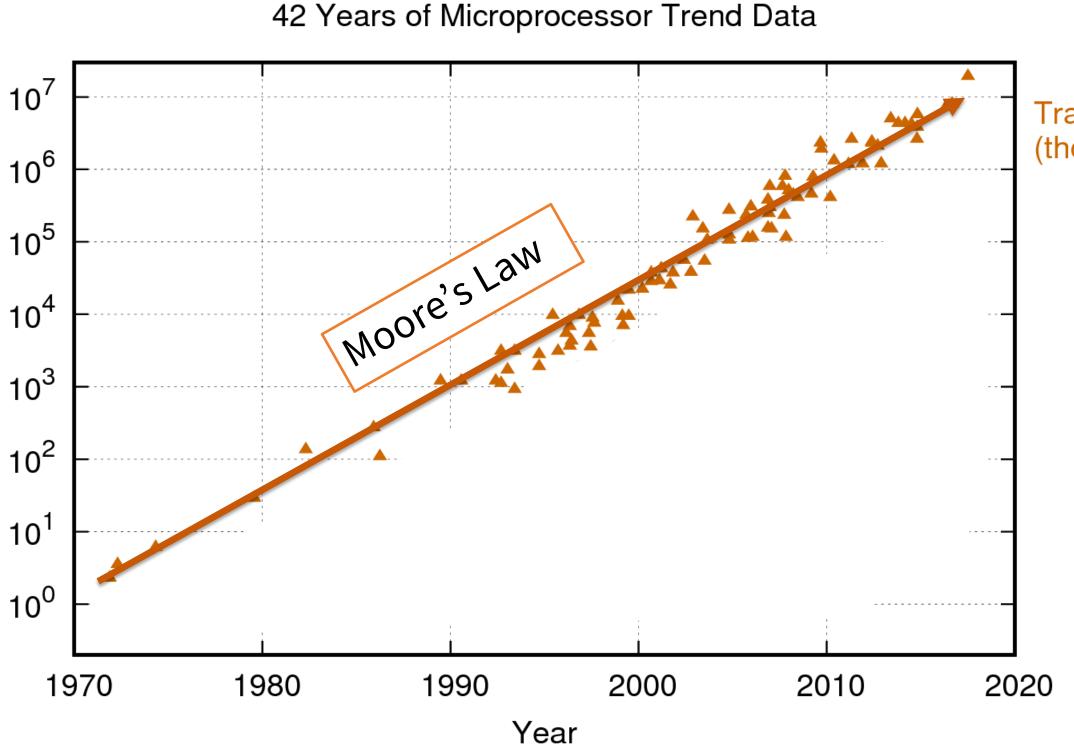

# Moore's Law: A remarkable journey

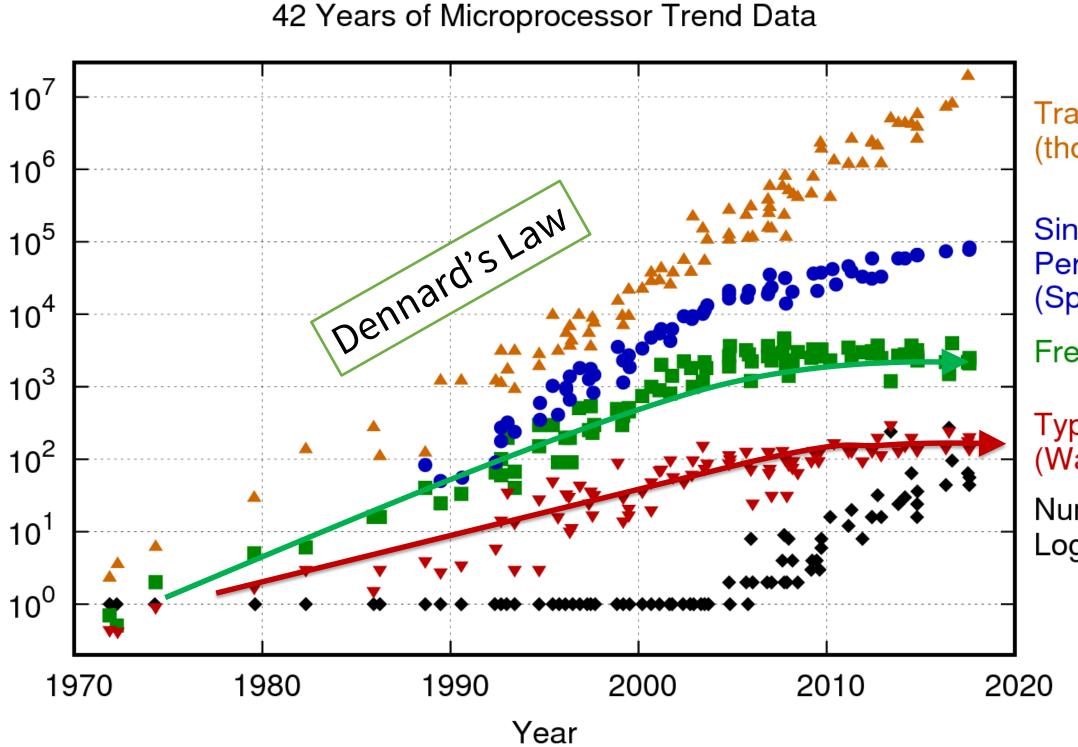

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2017 by K. Rupp data source: https://goo.gl/bb6wZW

Transistors (thousands)

....remarkable journey is described by Moore's Law, Intel co-founder Gordon Moore's 1967 prediction that the number of transistors we can pack into a microchip would double every 18-24 months.

**50 years of exponential growth!!**

Motivation

# All exponentials must end...

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2017 by K. Rupp data source: https://goo.gl/bb6wZW

Transistors (thousands)

Single-Thread Performance (SpecINT x 10<sup>3</sup>)

Frequency (MHz)

Typical Power (Watts)

Number of Logical Cores

"...the nature of exponentials is that you push them out and eventually disaster happens"

Some end sooner than others...Dennard's Law that says as transistors shrink, they get faster, use less power and get cheaper...ended about 10 years back!

Motivation

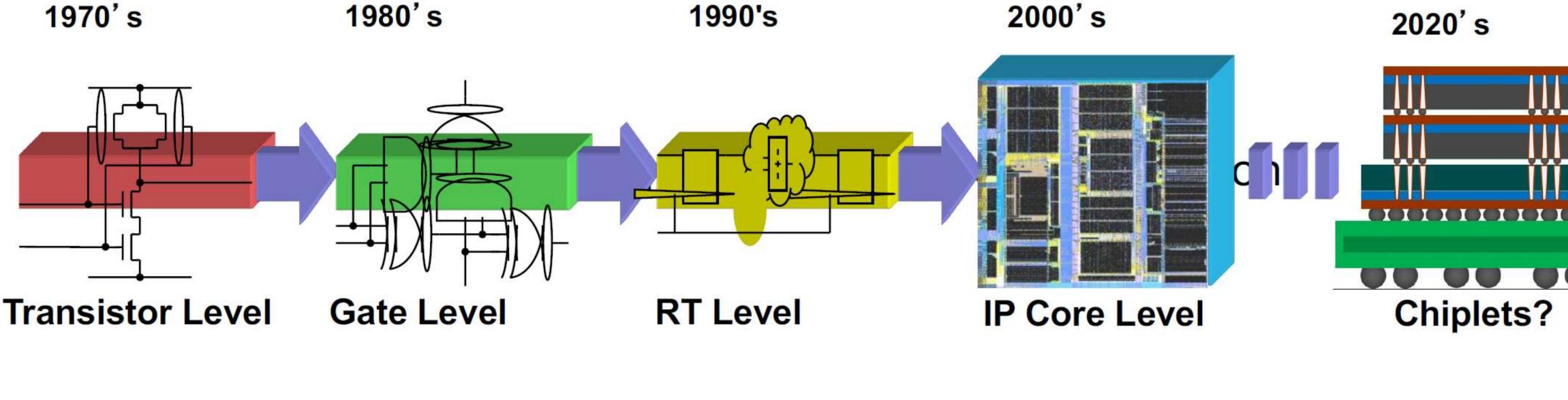

# Gordon Moore also said...

interconnected."

Electronics, volume 38, number 8, April 19, 1965

## **Open.** Together.

#### "It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and

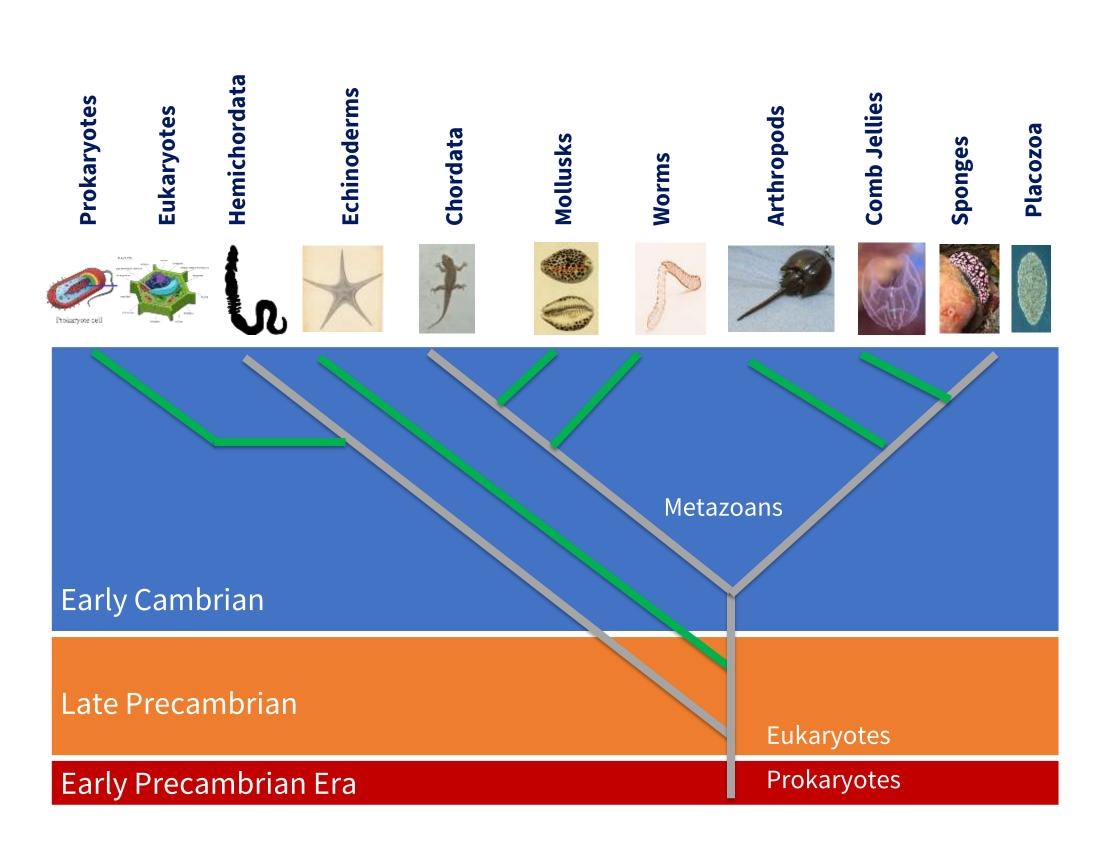

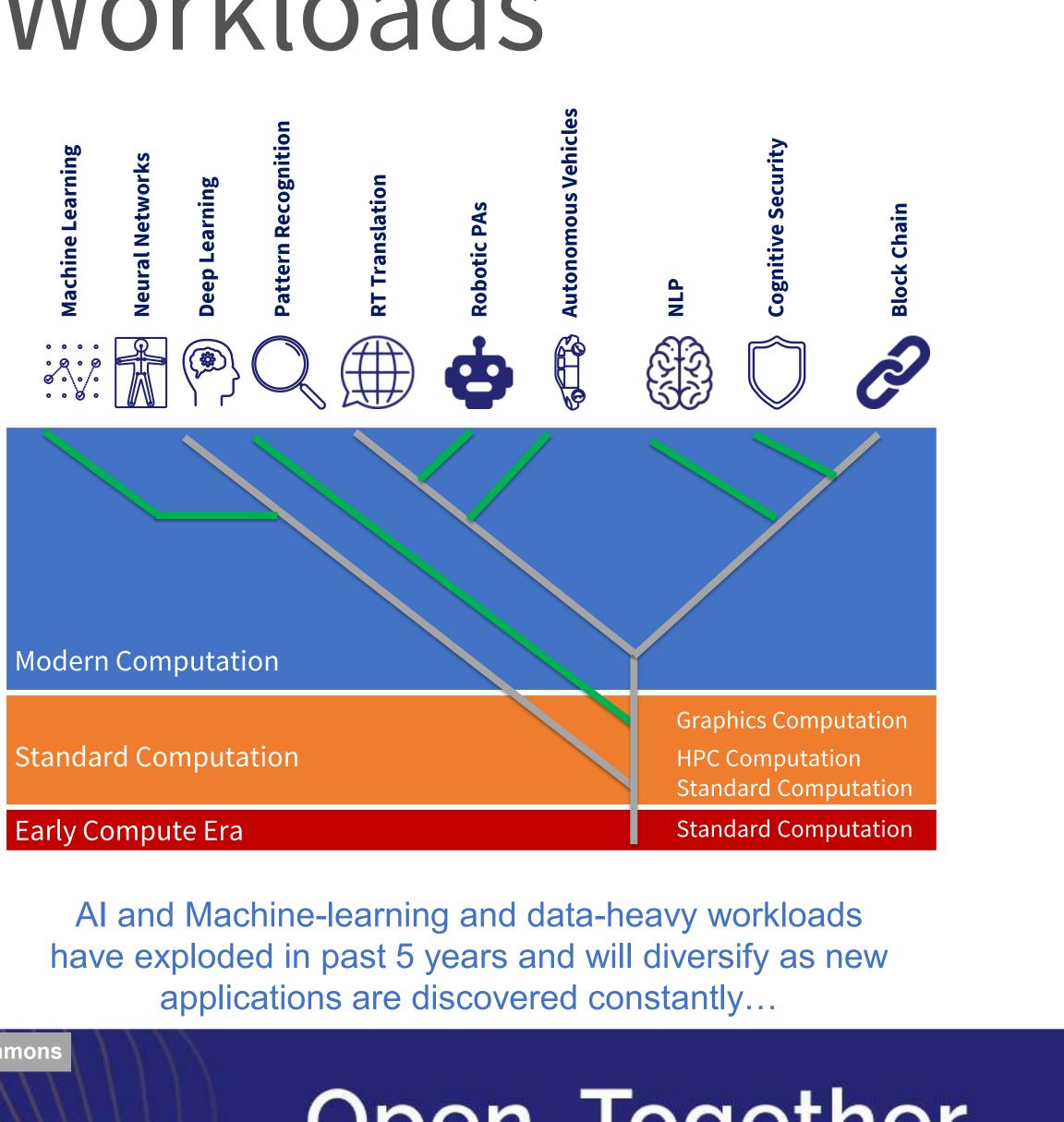

# Cambrian Explosion of Workloads

Bio-Diversity Exploded from single cells into multicell organisms during the Cambrian explosion; all major phylla were established in this transition

DCP REGIONAL SUMMIT

Open. Together.

**All images from Creative Commons**

# **Domain-Specific Architectures**

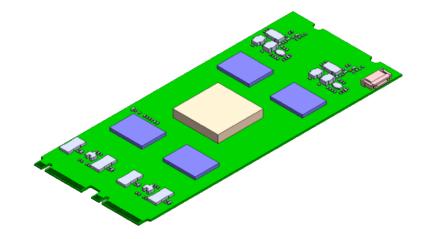

# Logic Disaggregation

Improve yield and simplify/relax design requirements

**IO Disaggregation**

Right functionality in right silicon node

[L. Su, IEDM'17]

# **Open Domain-Specific Architecture (ODSA)**

#### **CHIPLET APPROACH**

## **Open Domain-Specific Architectures**

CPU/GPU Combo

CPU Cores Combo

**Optimized** (Cost and Power)

Architecture

## **Open.** Together.

WIDE

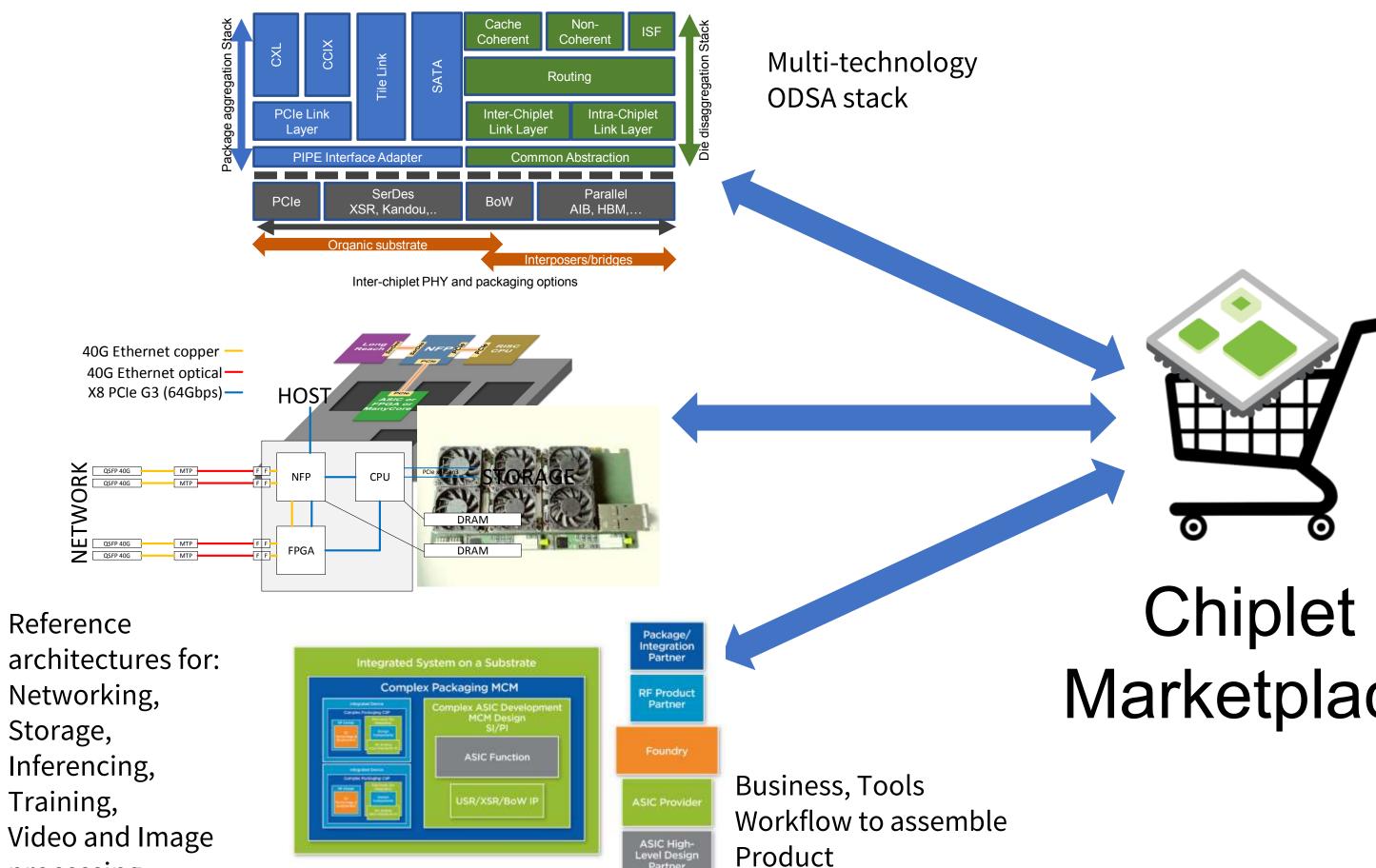

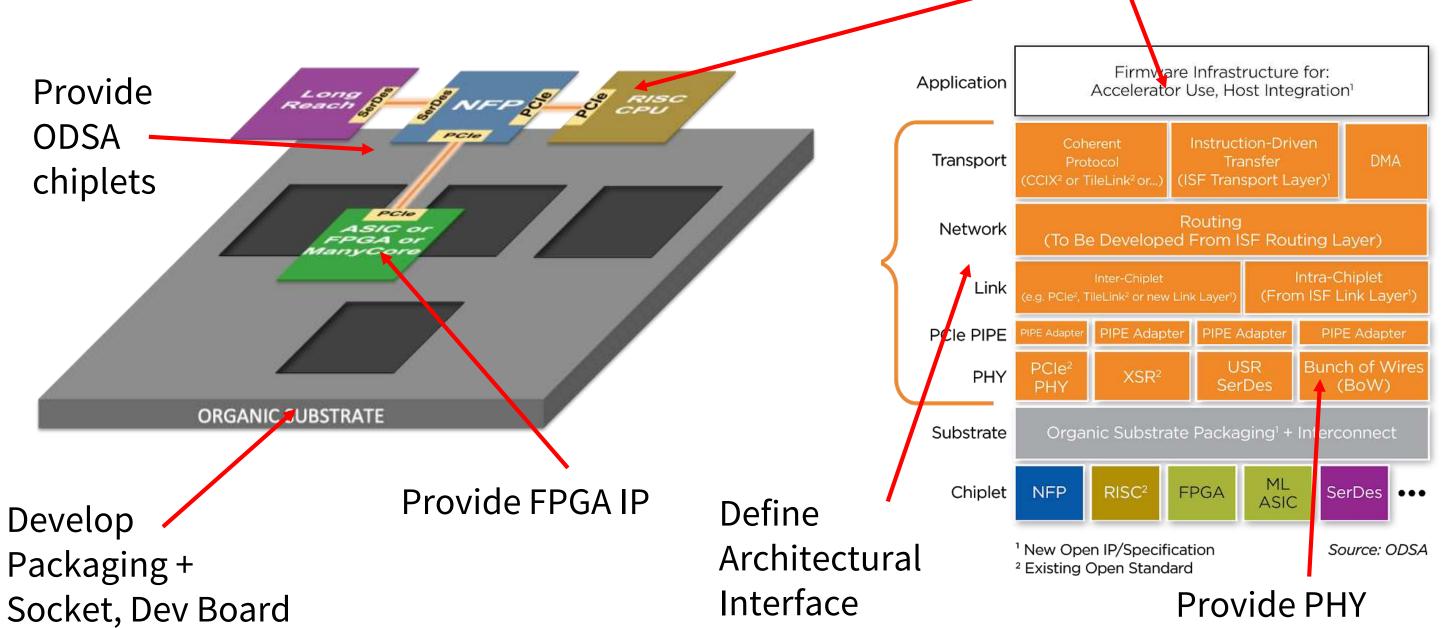

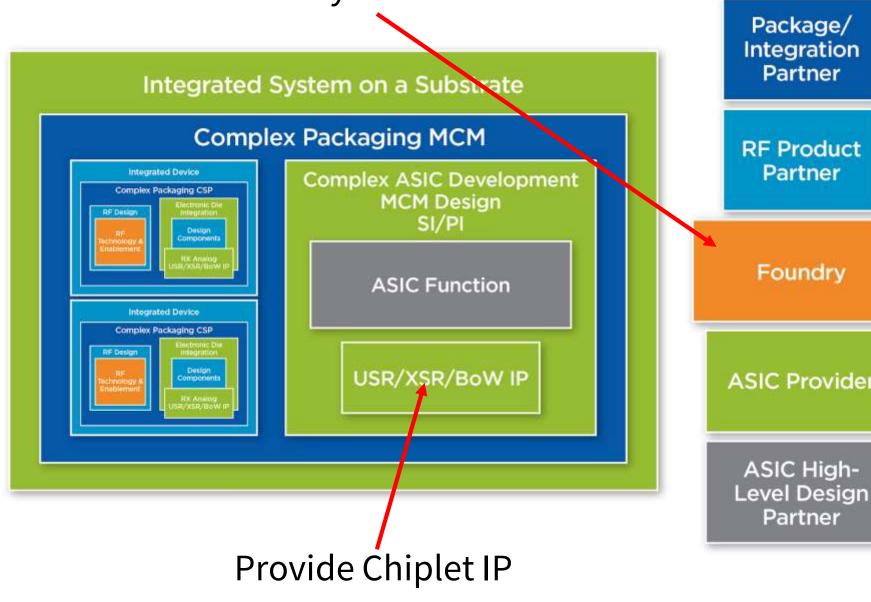

# **ODSA Goal: Chiplet Marketplace**

#### **ODSA** Activities

processing

# Marketplace

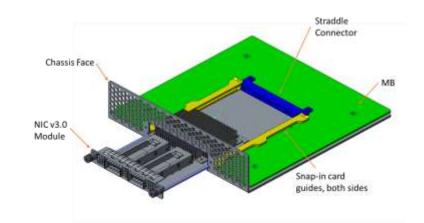

OCP Form Factors drive Power,I/O Footprint, Performance

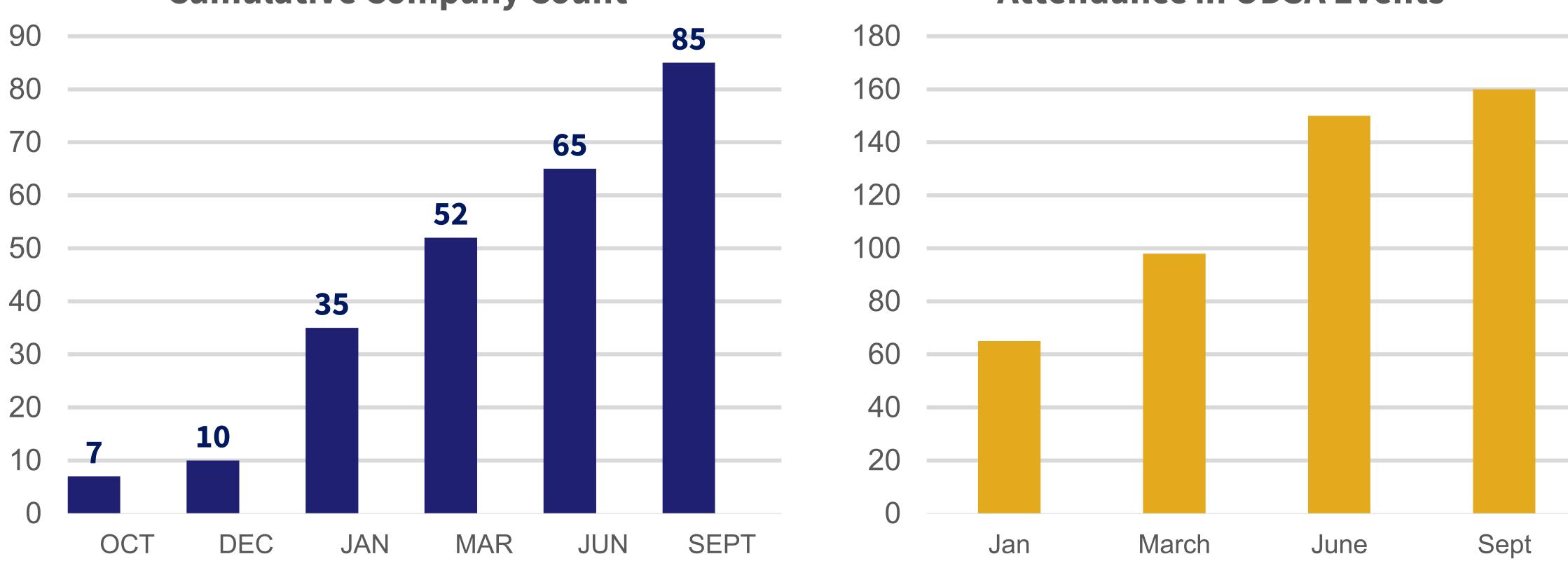

# Growth of ODSA

#### **Cumulative Company Count**

## Open. Together.

#### Source: OCP ODSA Survey

#### **Attendance in ODSA Events**

# **ODSA: A New Server Sub-Project**

#### **Extending Moore's Law:**

- Domain-Specific Architectures: Programmable ASICs to accelerate high-intensity workloads (e.g. Tensorflow, Network Flow Processor, Antminer...

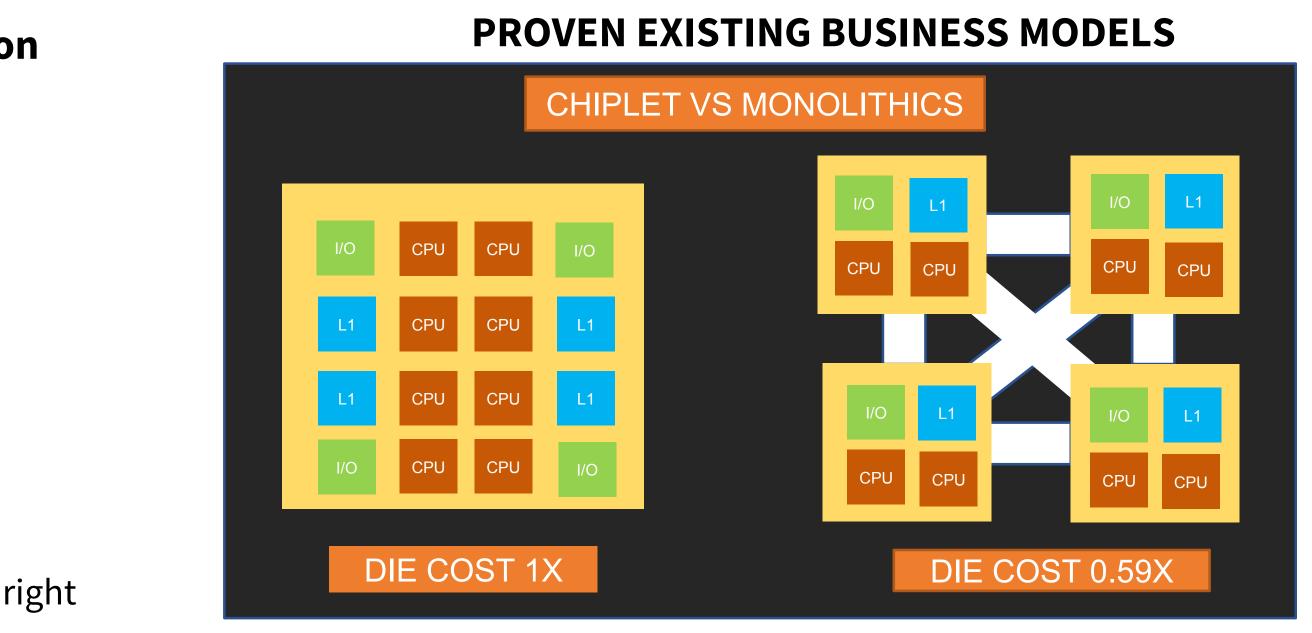

- Chiplets: Build complex ASICs from multiple die, instead of as monolithic devices, to reduce development time/costs and manufacturing costs.

#### **Open Domain-Specific Architecture: An architecture to build domain-specific products**

- Today: All multi-chiplet products are based on proprietary interfaces • Tomorrow: Select best-of-breed chiplets from multiple vendors • Incubating a new group, to define a new open interface, build a PoC

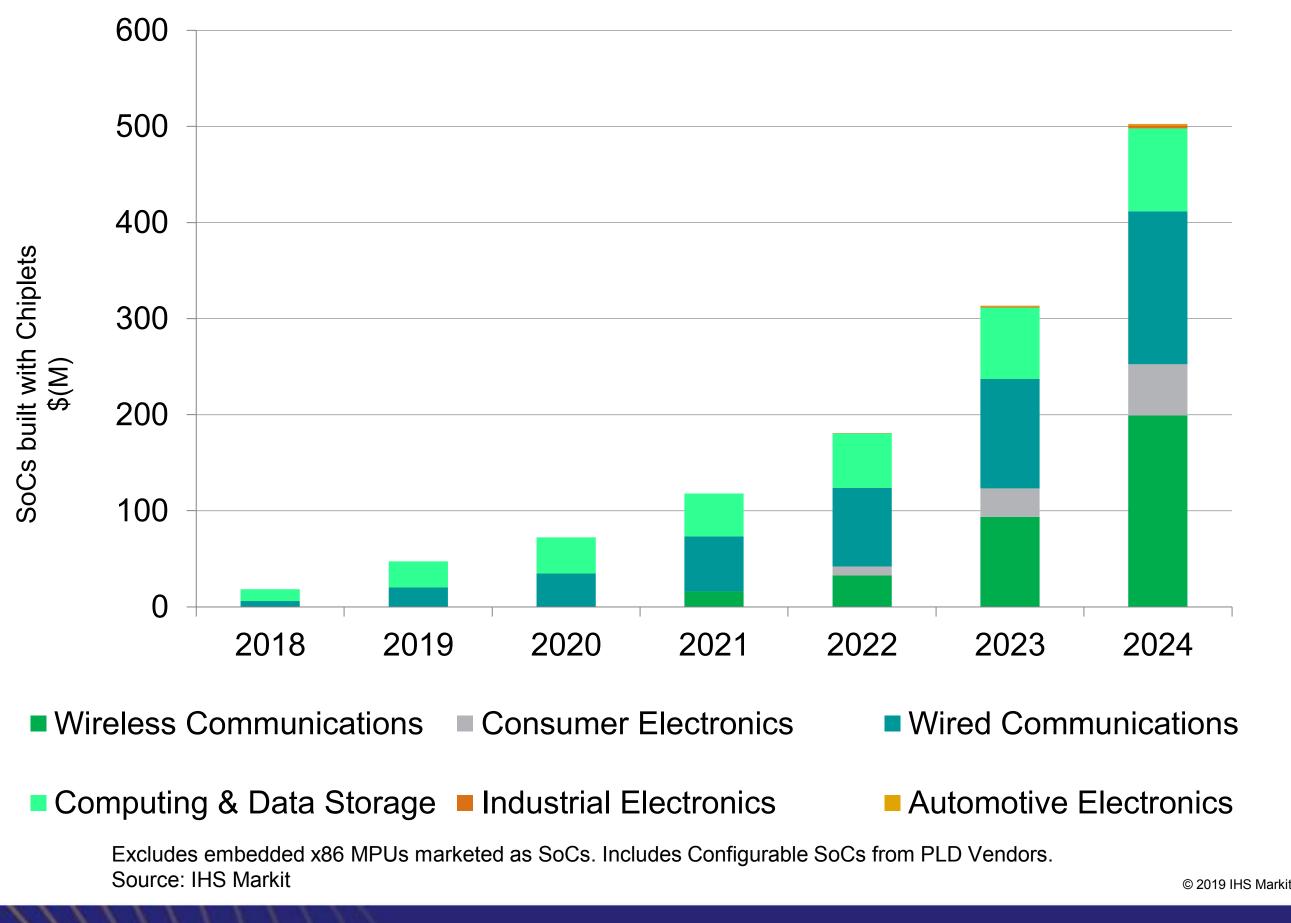

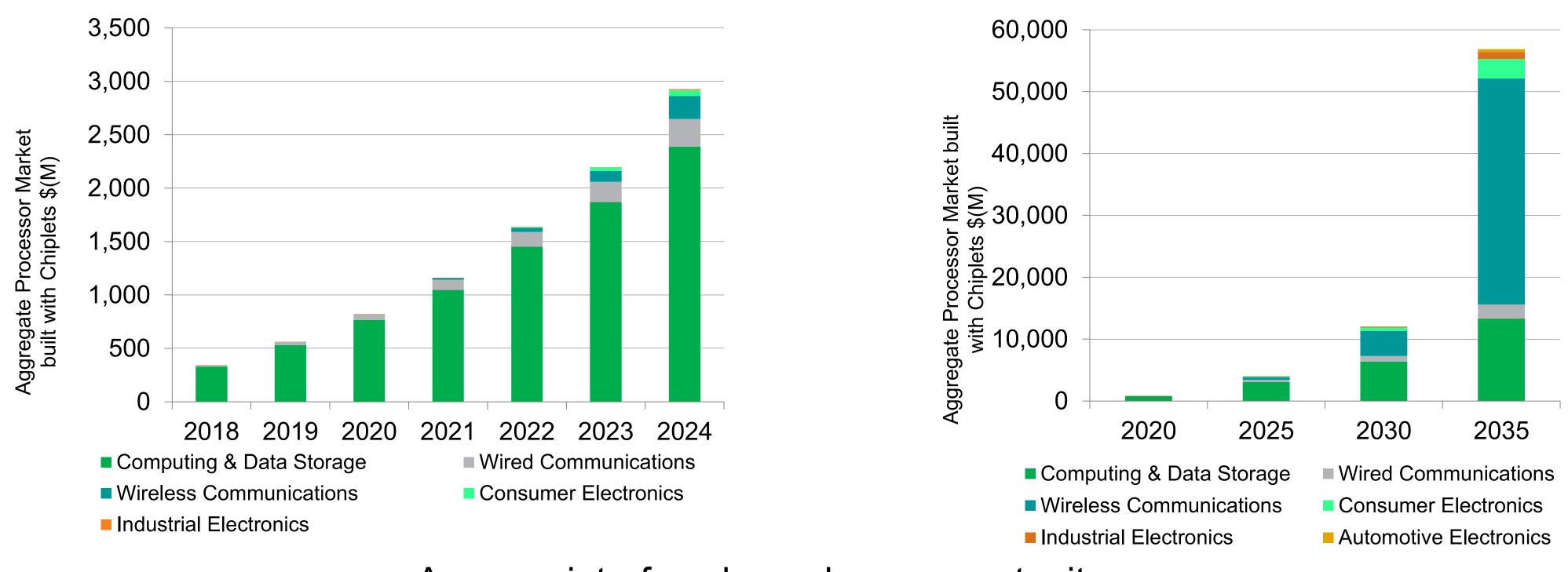

# The Tip of the Spear "Opportunity"

Independent research from IHS Markit

Four use cases for chiplets SoCs MPU GPU **PLDs**

Six Verticals (wireless, wireline, consumer, computing, industrial, automotive)

SoCs shown on the right. Immediate opportunity for an open interface – the tip of the spear.

#### SoC SAM by Market Segment

## The End Game

#### **Overall Chiplet SAM by Market Segment**

Initially dominated by compute uses case, other market segments grow to dominate

#### **Extended Chiplet SAM by market segment**

An open interface has a huge opportunity

# Please Help! Join a Workstream

Join the PoC, Build fast: (Quinn Jacobson/Jawad Nasrullah/ Jayaprakash Balachandran)

Join Interface/Standards: (Mark Kuemerle/Ramin Farjad/ Robert Wang/David Kehlet) Develop software

#### Join Business, IP and workflow: (Sam Fuller/Dharmesh Jani)

Define test and assembly workflow

## technology

Workstream contact information at the ODSA wiki

# Active Projects

| Project                    | Objective                                                                        | Organizations Participating                                                                                                                                                                 | Recent Results                                            | Upcoming Milestones                          | Needs                                                      |

|----------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------|------------------------------------------------------------|

| PHY Analysis               | PHY requirements<br>PHY analysis<br>Cross-PHY abstraction (PIPE)                 | Alphawave, AnalogX,<br>Aquantia, Avera Semi,<br>Facebook, Intel, Kandou,<br>Netronome, zGlue,                                                                                               | PHY Analysis paper<br>(published at Hot Interconnect)     | PIPE abstraction                             |                                                            |

| BoW Interface              | No technology license fee, easy to port inter-chiplet interface spec             | Aquantia, Avera Semi,<br>Netronome                                                                                                                                                          | BoW Interface proposal<br>(published at Hot Interconnect) | BoW specification 0.7<br>End September, 2019 | Test chips, Chiplet library supporting interface           |

| Prototype                  | product that integrates existing die from<br>multiple companies into one package | Achronix, Cisco, Netronome,<br>NXP, Samtec, Sarcina, zGlue,<br>Macom, Facebook                                                                                                              | Decomposable design flow.                                 | Committed schedule                           | End user<br>End user participation<br>~30% funding is open |

| Chiplet design<br>exchange | Open chiplet physical description format.                                        | Ayar, NXP, zGlue,                                                                                                                                                                           | Draft spec                                                | ZEF Exchange format draft specification      |                                                            |

| Link and Network<br>Layer  | Interface and implementations – requirements and proposals                       | Achronix, Avera Semi, Intel,<br>Netronome, NXP, Xilinx                                                                                                                                      |                                                           |                                              |                                                            |

| Multi-chiplet test         | Test requirements for an open-chiplet interface                                  | Engineers from:<br>Achronix, AnalogX, ASE, Avera Semi, Ayar, Cisco, Facebook,<br>Ferric, Intel, Kandou, Macom, Marvel, Netronome, NXP, On Semi,<br>Samtec, Sarcina, Synopsys, Xilinx, zGlue |                                                           |                                              |                                                            |

| Chiplet monitoring         | Monitoring infrastructure for chiplet operation                                  |                                                                                                                                                                                             |                                                           |                                              |                                                            |

| Business workflow          | Formalize learnings from prototype effort                                        |                                                                                                                                                                                             |                                                           |                                              |                                                            |

Wiki: <u>https://www.opencompute.org/wiki/Server/ODSA</u>, meet Fridays at 8 AM Pacific Time. Please join us.

#### AFRICAN PROVERB

#### IF YOU WANT TO GO FAST, GO ALONE IF YOU WANT TO GO FAR, GO TOGETHER

# Open. Together.

**OCP Regional Summit** 26-27, September, 2019