# Welcome

OCP ODSA Project Workshop September 12, 2019

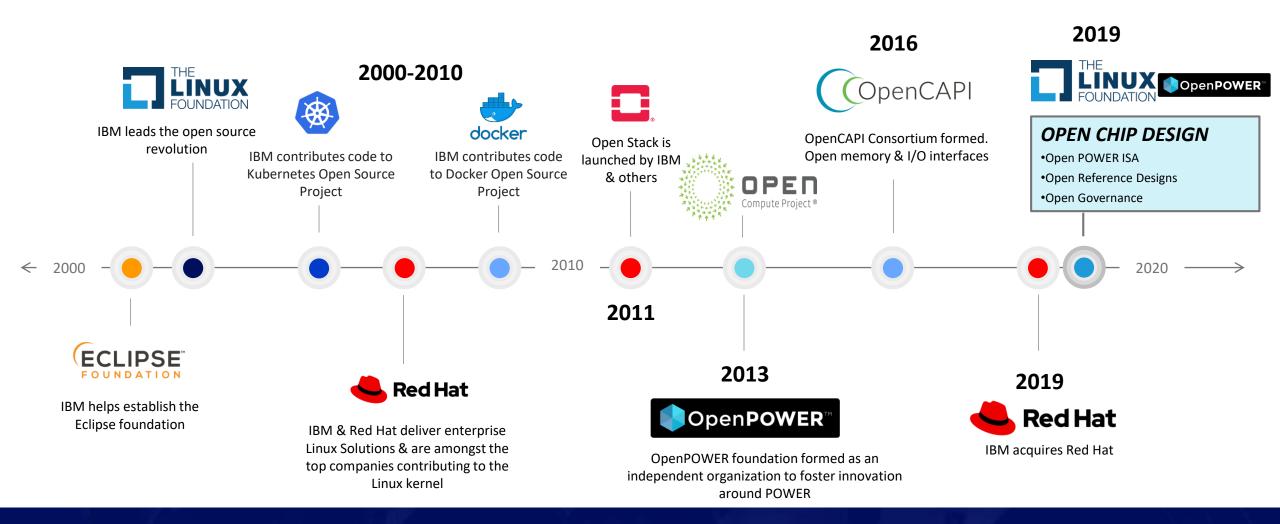

### IBM has a long history in supporting open initiatives...

### IBM expands open hardware ecosystem with major contributions to community

OpenPOWER Summit NA August 20, 2019

#### **Open POWER ISA:**

Opening POWER Instruction Set Architecture (ISA), inclusive of patent rights.

#### **Open Reference Designs:**

Open sourcing a softcore implementation of the POWER ISA as well as reference designs for the architectureagnostic Open Coherent Accelerator Processor Interface (OpenCAPI) and Open Memory Interface (OMI).

#### **Open Governance:**

OpenPOWER Foundation joining the Linux Foundation

### Where can I find?

OpenPOWER Foundation https://openpowerfoundation.org/

OpenPOWER Summit EU 2019 – October 31-November 1 Register Today! <u>https://events.linuxfoundation.org/events/openpower-summit-eu-2019/</u>

OpenCAPI Consortium https://opencapi.org/

POWER ISA Softcore https://github.com/antonblanchard/microwatt

OpenCAPI and OMI Reference Designs – Going live today! <u>https://github.com/OpenCAPI</u> OpenCAPI3.0\_Device\_RefDesign omi\_host\_fire omi\_device\_ice

## Exploiting Composable Heterogeneity through Open Architectures

Jeff Stuecheli Josh Friedrich

## Chiplet Design Opportunities

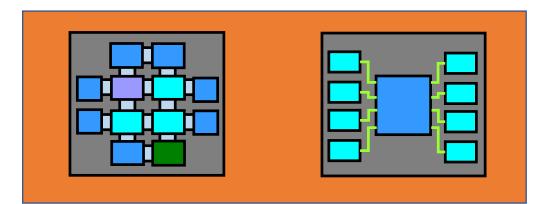

### Chip disaggregation

- Cost reduction

- Modularity

- Optimized technology use

- Latency reduction

### System integration

- More efficient connectivity

- Overcome reticle limit

- Increased system density

- Heterogenous integration

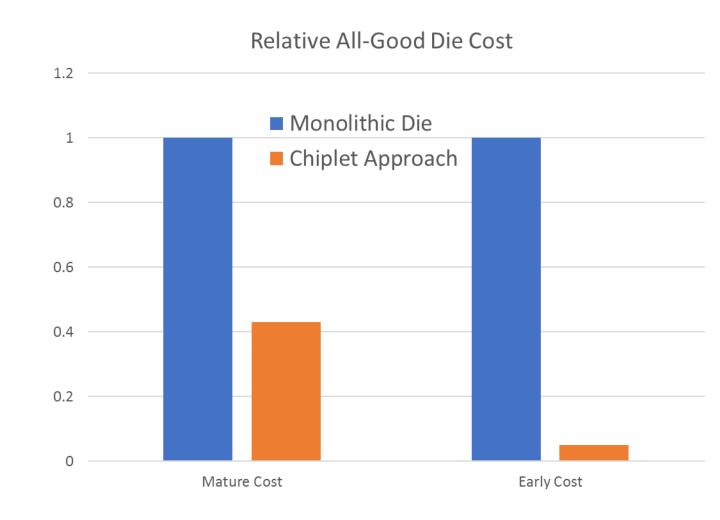

### Chiplet Benefits: Cost

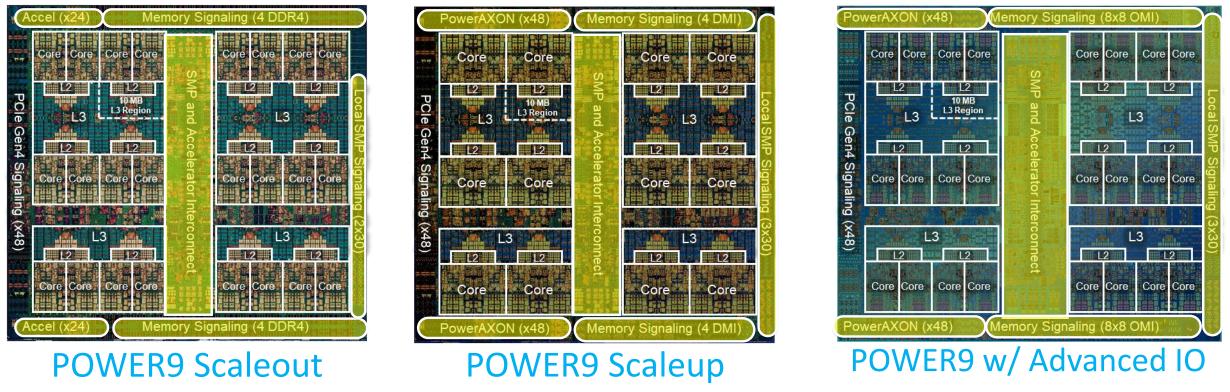

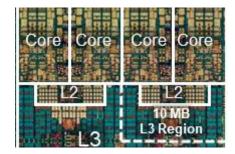

## Chiplet Benefits: SoC Modularity POWER9 Processor Family

- Any revision requires new processor tapeout, test pattern generation, and qualification.

- Integration of new IP can create disruptive changes to chip infrastructure.

- Moving any IP to next technology requires full chip to be re-designed for next node.

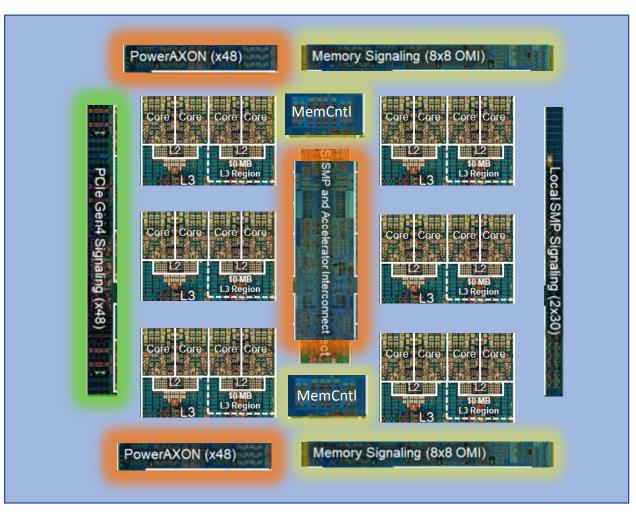

### Chiplet Benefits: Potential Package-Level Modularity

- IP providers deliver tested physical chiplet vs. design IP needing integration

- Avoids time-consuming & expensive re-integration into SoC

- Durable IP blocks avoid change

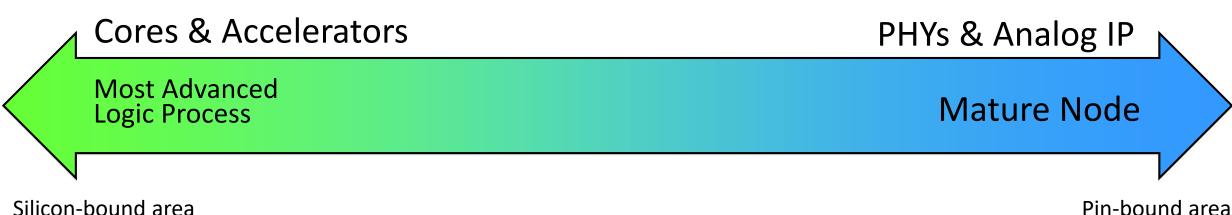

## Chiplet Benefits: Technology Use Optimization

Silicon-bound area

Base technology elements (logic devices, SRAMs)

Power/performance sensitive

Functionally resilient to model inaccuracy

Rich technology menu (passives, multi-oxide, etc)

Low power density

Functionally sensitive to model-to-hardware

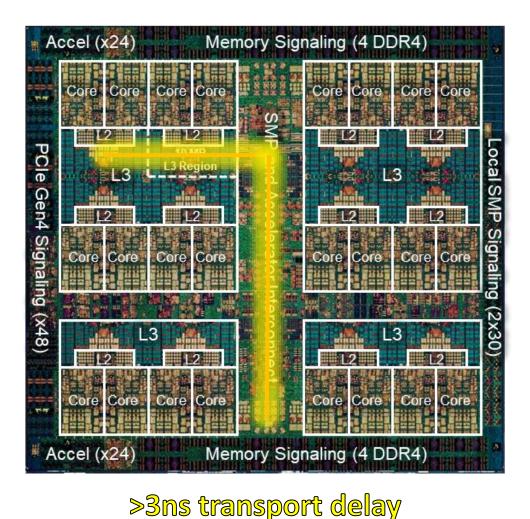

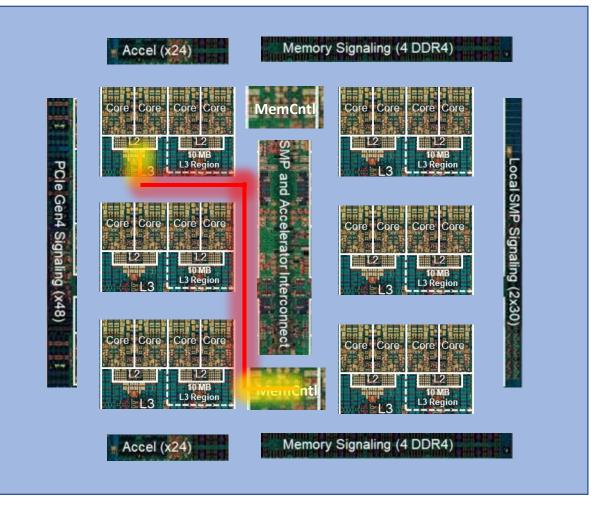

### Chiplet Benefits: Latency Optimization

#### ~0.5ns transport delay

Module wiring offers >10x advantage in time of flight over best on-chip transport.

## Chiplet Design Opportunities

### Chip disaggregation

- Cost reduction

- Modularity

- Optimized technology use

- Latency reduction

### System integration

- More efficient connectivity

- Overcome reticle limit

- Increased system density

- Heterogenous integration

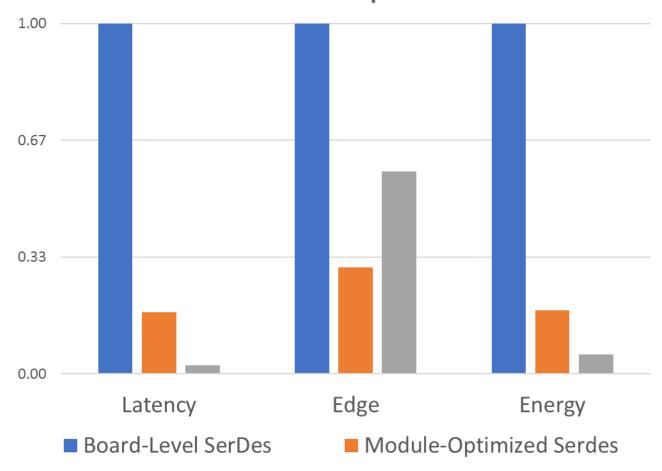

## Chiplet Benefits: More Efficient Connectivity

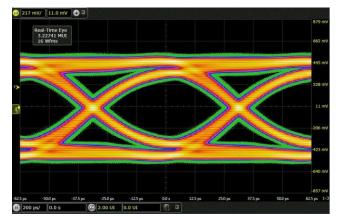

Board level integration requires robust SERDES to handle complex channels, minimize wire counts, etc.

Chiplet provides opportunity to significantly improve connectivity

Need a range of options to optimize latency, power, and chip resources

■ Wide, On-module Bus

Interface Comparison

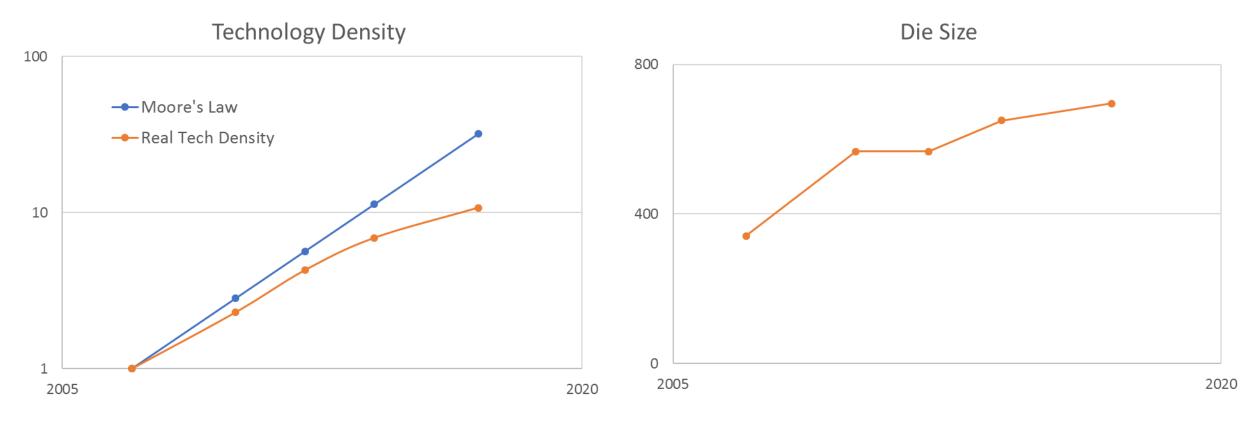

### Chiplet Benefits: Breaking Reticle Limit

SoC integration is limited by transistors in the reticle.

As density improvement has slowed, die size has grown to compensate, but this is approaching its limit. Integration leveraging advanced packaging technologies and chiplet design provides an anecdote.

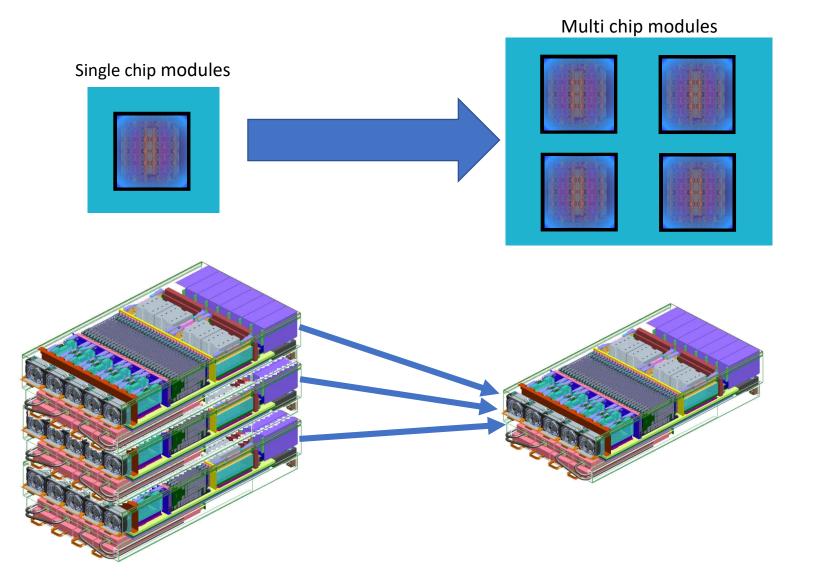

### Chiplet Benefits: Increased Density

Simple opportunity created by exceeding the reticle is to increase compute density, but this approach has limits.

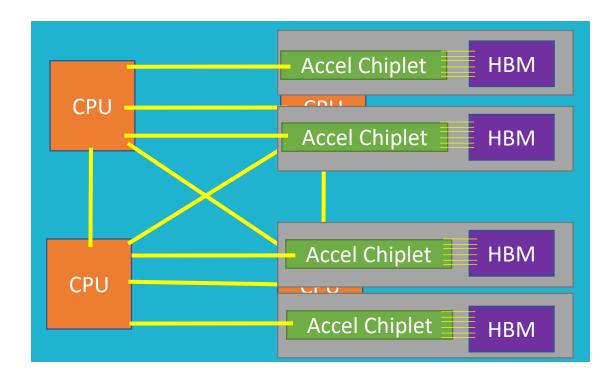

### Chiplet Benefits: Heterogenous Integration

Leverage heterogenous chiplets to deliver value

- Right compute for all facets of a job

- Diverse technologies to maintain system balance

- Extreme connectivity through advanced packaging

- Simpler demands on IP chiplet providers vs. delivering full SoC

### Chiplet Challenges & Requirements

Broad range of packaging innovation

• Open PHY & protocol standards

Cooling & current delivery

Robust test infrastructure

Standards + tooling

Business ecosystem

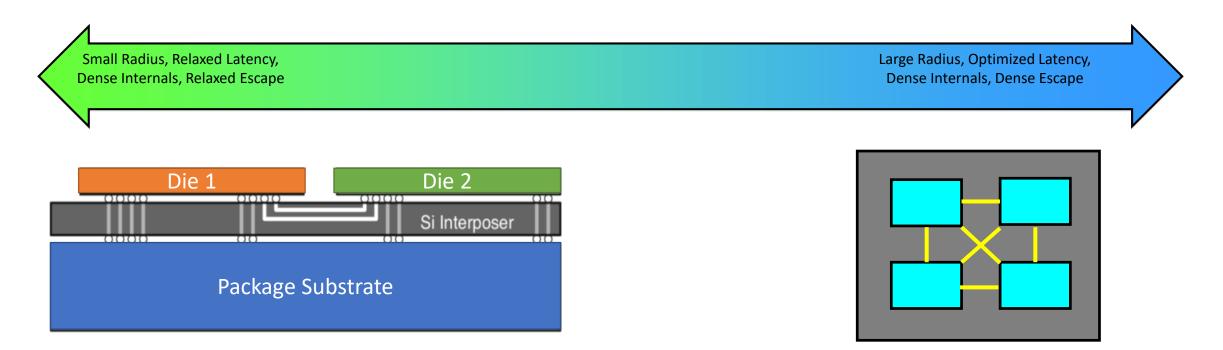

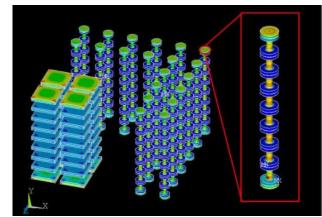

### **Chiplet Requirements:** Packaging & Silicon Aggregation Innovations

Silicon Area per Module: Depends on laminate capability, yield, manufacturing economics

End-to-end Intra-connect Latency: Depends on total silicon radius, internal/external bandwidth

External Bandwidth Escape: Depends on internal/external Intra-connect split, system interface rqmts

Internal Bandwidth Density: Depends on internal/external Intra-connect split, system interface rqmts

Granularity of Composability: Depends on chipset flexibility and composability rqmts

Technology optimization varies depending on silicon, latency, and bandwidth needs:

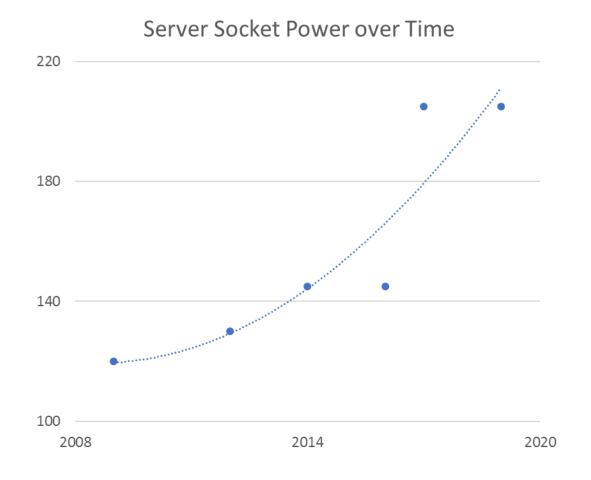

## Chiplet Requirements: Cooling & Current Delivery

- Power/socket has grown significantly over the last decade.

- Power/socket growth will continue to accelerate.

- Slowing silicon scaling

- Vmin limitations

- Dense compute acceleration

- Chiplet design adds significant complexities.

- Greater than reticle integration

- Large instantaneous currents from IP activity changes

- Large # of voltage supplies to support heterogenous IP

- Continued investment in solutions is necessary.

- Cost-effective cooling solutions

- Efficient in-package voltage regulation

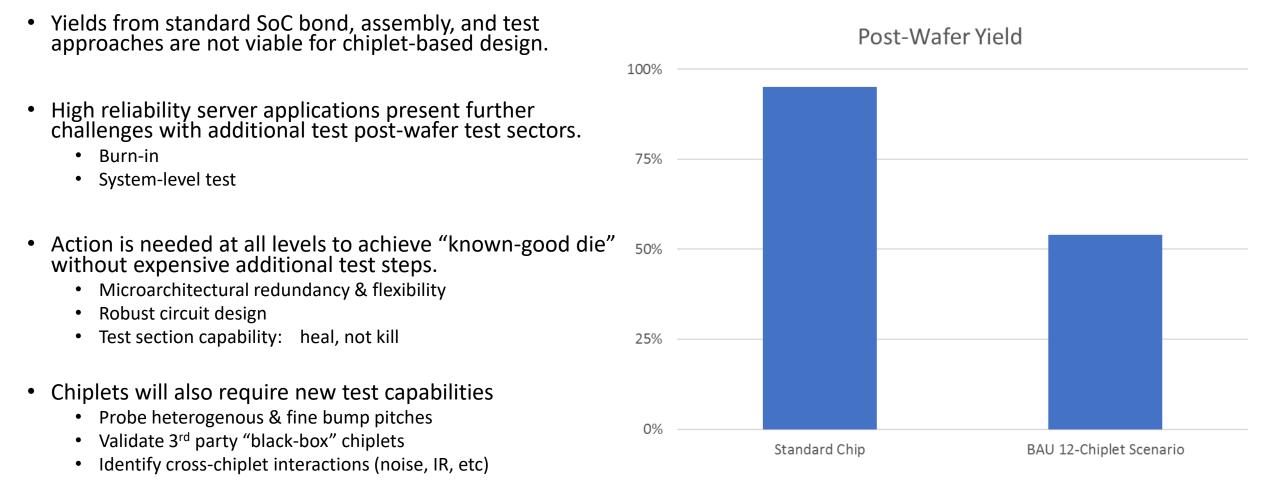

### Chiplet Requirements: Test Innovation

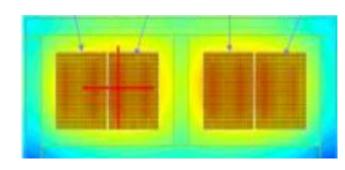

### Chiplet Requirements: Standards & Tooling

- Robust support for today's SoC ecosystem

- Standards: VHDL/Veriflog, Oasis/GDS, UPF,

- Tooling: DRC, LVS, ERC, static timing, noise, power, thermal, etc.

- Similar support needed to support rapid integration of chiplets at package level

- Power & thermal models for cooling & current delivery

- Electrical models for noise analysis and signal integrity

- Mechanical models to study package stress

**Thermal Models**

#### Signal Integrity

#### **Mechanical Stress**

### Chiplet Requirements: Business Models

### **Opportunities**

Improved solutions Increased volume

Focused investment

\_. . . . .

Time-to-market

### Challenges

Supply chain continuity Test ownership Field support & debug Warranty & liability Chiplet Requirements: Open Interconnect Protocol

- Architecture agnostic

- Asymmetric

- Latency optimized

- Flexible

- Robust, silicon-proven

### Open Standards for Servers

- Diss-aggregation of chiplets into customized form factors

- CPU socket,

- Memory DIMM: Existing standards difficult specialize

- Determinism prevents flexibility

- PCIe: Open standard with long standing compatibility and flexibility

- high latency in hw and sw

- Limited power and cooling

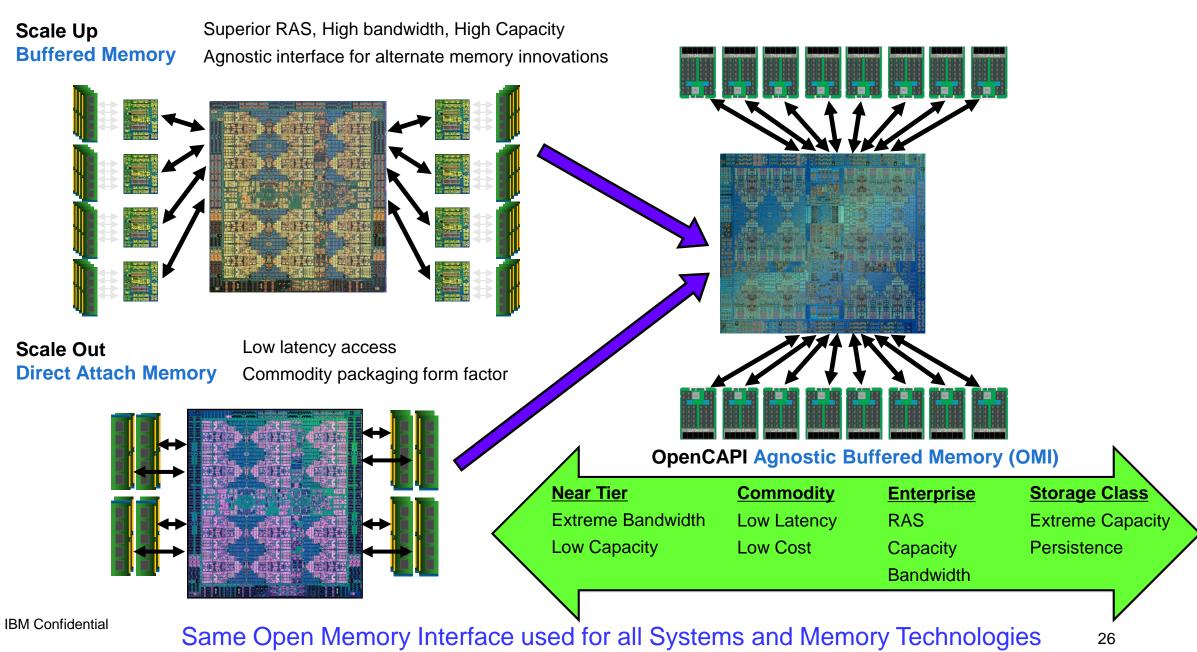

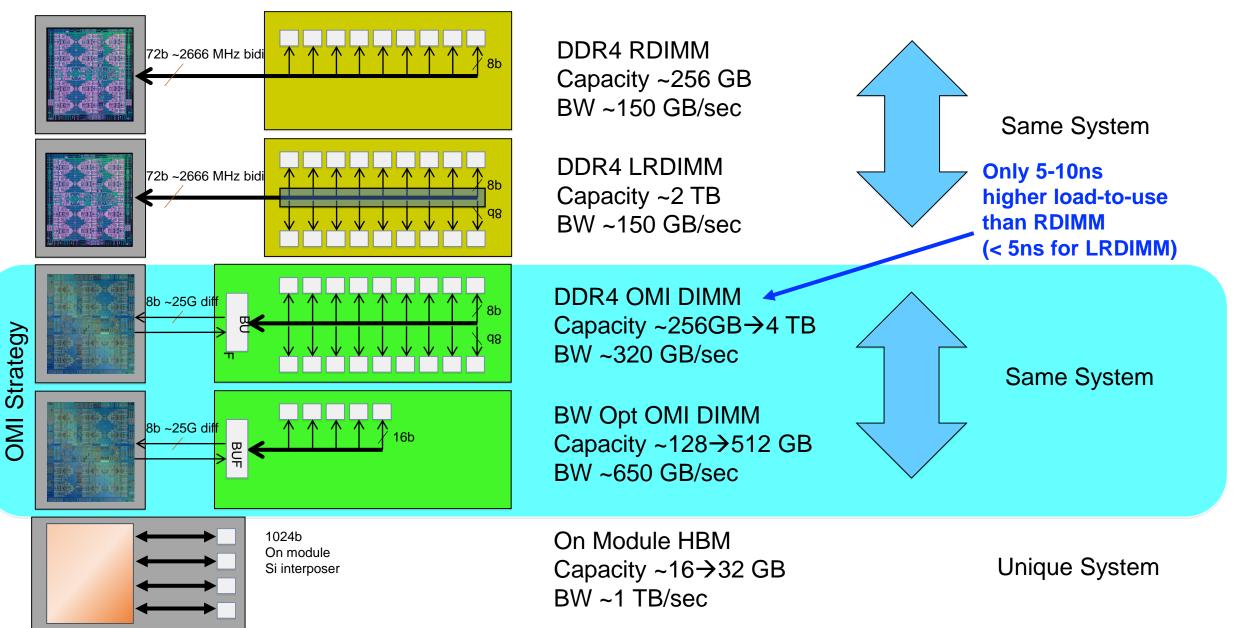

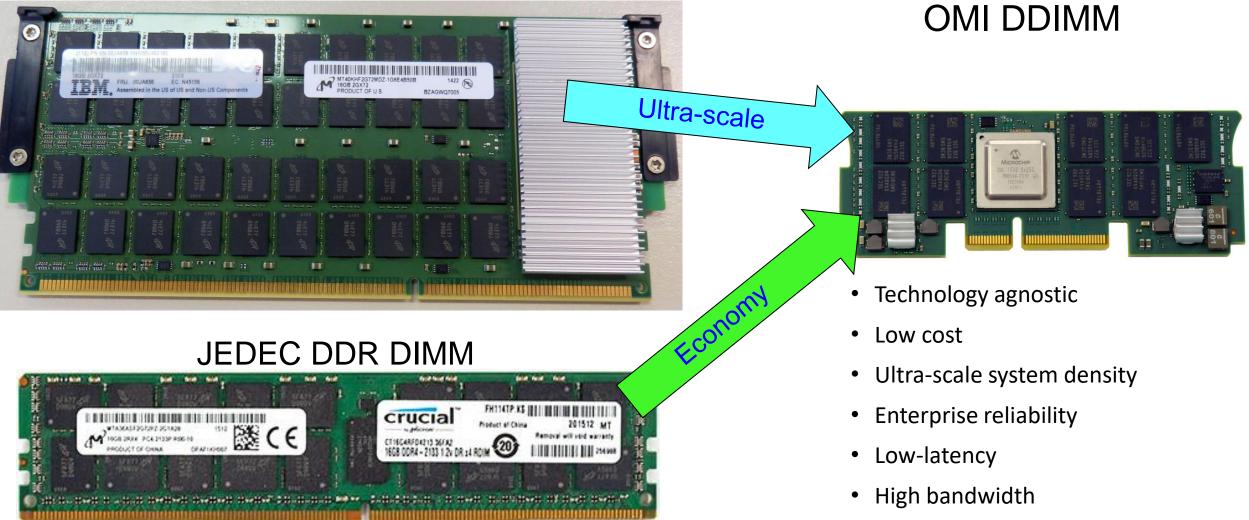

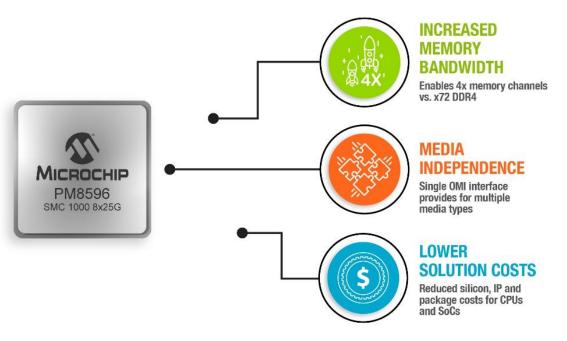

- OMI (Open Memory Interface): Enables flexible memory standards

- SerDes protocol provided ~5x reduction in host IO overhead

- OAM: Emerging standard has great potential

- One physical standard, multiple DL/TL.

- Variability in protocol and topology complicates systems

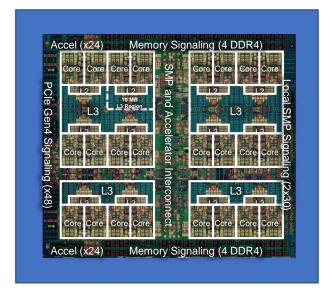

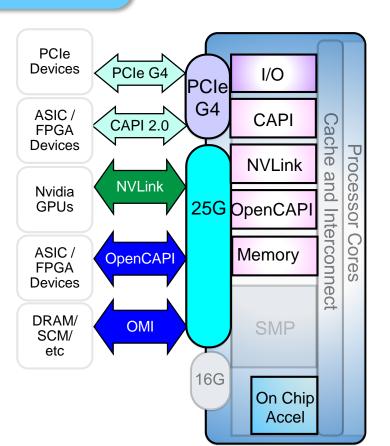

### POWER9 – Acceleration Platform

- Extreme Processor / Accelerator Bandwidth and Reduced Latency

- Coherent Memory and Virtual Addressing Capability for all Accelerators

- OpenPOWER Community Enablement Robust Accelerated Compute Options

- State of the Art I/O and Acceleration Attachment Signaling

- PCle Gen 4 x 48 lanes 192 GB/s duplex bandwidth

- 25 G Common Link x 96 lanes 600 GB/s duplex bandwidth

- <u>Robust Accelerated Compute Options with OPEN standards</u>

- **On-Chip Acceleration** Gzip x1, 842 Compression x2, AES/SHA x2

- CAPI 2.0 4x bandwidth of POWER8 using PCIe Gen 4

- NVLink Next generation of GPU/CPU bandwidth

- **OpenCAPI** High bandwidth, low latency and open interface

- **OMI** High bandwidth and/or differentiated for acceleration

#### 25

**POWER9**

**PowerAccel**

#### **POWER9 Family Memory Architecture**

### **Primary Tier Memory Options**

### **DRAM DIMM Comparison**

#### IBM Centaur DIMM

### **Open Memory Interface (OMI)**

- Signaling: 25.6GHz vs DDR4 @ 3200 MHz

- 4x raw bandwidth per I/O signal

- 1.3x mixed traffic utilization

- Idle load-to-use latency over traditional DDR:

- POWER8/9 Centaur design ~10 ns

- OMI target of ~5-10 ns (RDIMM)

- OMI target of < 5ns (LRDIMM)

- IBM Centaur: One proprietary DMI design

- Microchip SMC 1000:

- Open (OMI) design

- Emerging JEDEC Standard

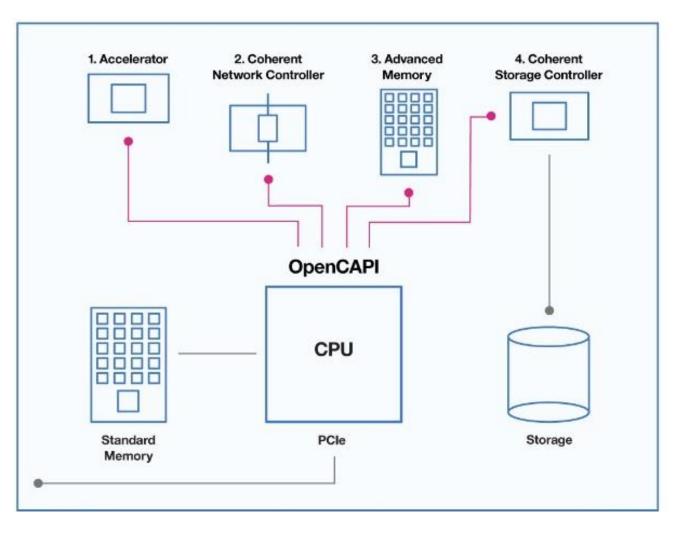

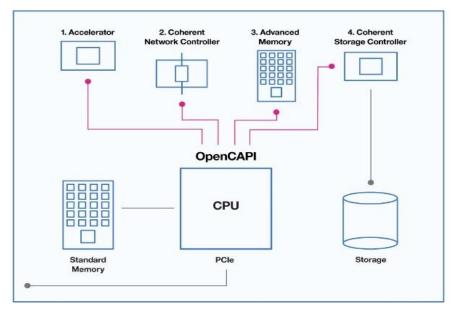

### **OpenCAPI Design Goals**

- Designed to support range of devices

- Coherent Caching Accelerators

- Network Controllers

- Differentiated Memory

- High Bandwidth

- Low Latency

- Storage Class Memory

- Storage Controllers

- Asymmetric design, endpoint optimized for host and device attach

- **ISA of Host Architecture**: Need to hide difference in Coherence, Memory Model, Address Translation, etc.

- **Design schedule:** The design schedule of a high performance CPU host is typically on the order of multiple years, conversely, accelerator devices have much shorter development cycles, typically less than a year.

- Timing Corner: ASIC and FPGA technologies run at lower frequencies and timing optimization as CPUs.

- **Plurality of devices:** Effort in the host, both IP and circuit resource, have a multiplicative effect.

- Trust: Attached devices are susceptible to both intentional and unintentional trust violations

- Cache coherence: Hosts have high variability in protocol. Host cannot trust attached device to obey rules.

#### **OpenCAPI 4.0: Asymmetric Open Accelerator Attach**

#### **Roadmap of Capabilities and Host Silicon Delivery**

| Accelerator Protocol      | CAPI 1.0               | CAPI 2.0               | OpenCAPI 3.0                | OpenCAPI 4.0                | OpenCAPI 5.0                   |

|---------------------------|------------------------|------------------------|-----------------------------|-----------------------------|--------------------------------|

| First Host Silicon        | POWER8<br>(GA 2014)    | POWER9 SO<br>(GA 2017) | POWER9 SO<br>(GA 2017)      | POWER9 AIO<br>(GA 2020)     | POWER10<br>(GA 2021)           |

| Functional Partitioning   | Asymmetric             | Asymmetric             | Asymmetric                  | Asymmetric                  | Asymmetric                     |

| Host Architecture         | POWER                  | POWER                  | Any                         | Any                         | Any                            |

| Cache Line Size Supported | 128B                   | 128B                   | 64/128/256B                 | 64/128/256B                 | 64/128/256B                    |

| Attach Vehicle            | PCle Gen 3<br>Tunneled | PCle Gen 4<br>Tunneled | 25 G (open)<br>Native DL/TL | 25 G (open)<br>Native DL/TL | 32/50 G (open)<br>Native DL/TL |

| Address Translation       | On Accelerator         | Host                   | Host (secure)               | Host (secure)               | Host (secure)                  |

| Native DMA to Host Mem    | No                     | Yes                    | Yes                         | Yes                         | Yes                            |

| Atomics to Host Mem       | No                     | Yes                    | Yes                         | Yes                         | Yes                            |

| Host Thread Wake-up       | No                     | Yes                    | Yes                         | Yes                         | Yes                            |

| Host Memory Attach Agent  | No                     | No                     | Yes                         | Yes                         | Yes                            |

| Low Latency Short Msg     | 4B/8B MMIO             | 4B/8B MMIO             | 4B/8B MMIO                  | 128B push                   | 128B push                      |

| Posted Writes to Host Mem | No                     | No                     | No                          | Yes                         | Yes                            |

| Caching of Host Mem       | RA Cache               | RA Cache               | No                          | VA Cache                    | VA Cache                       |

## Summary: Taking a step back...

- Disaggregation trend

- ~Rack scale: Separate components into pools

- Memory, CPU, GPU, storage

- Enables agile deployment

- Interface Goal: Make ~rack scale appear as board level

- Chiplet trend

- Example: SOC like, but only build what is needed, buy standard components.

- Interface Goal: On die like communication (energy, bandwidth)

- Shared goals

- Heterogeneous Si

- Efficient flexible protocol layers

- Probably on application optimized physical layer