# OPEN POSSIBILITIES.

### Data Center-Secure Control Module 2.0 Specification Update

### **DC-SCM 2.0 Specification Update**

Qian Wang, Software Architect, Intel

Tim Lambert, Distinguished Engineer, Dell EMC

#### **OPEN POSSIBILITIES.**

### DC-SCM2.0 Overview

A collaboration to expand upon the DC-SCM 1.0 specification to allow for future scalability and longevity across multiple generations of enterprise platforms. To support evolving manageability interfaces, range of entities being securely managed and forthcoming use cases such as multi-node server designs.

# DC-SCM 2.0 changes from 1.0

- "Plug & Code" model to achieve universality among Host Processor Modules (HPM) and DC-SCMs

- Evolved interfaces for broader and future looking use cases with more typical examples toward maximizing interoperability

- Refined power states, limits and discovery rules for improved electrical compatibilities

- Overlayed dual-node alternate pin definition

- Evolved high-speed serial interface & protocol (LTPI) for pin reduction, remote BMC peripheral expansion & low latency transfers

- Mechanical foolproof break in compatibility between 1.0 & 2.0 (connector skew)

### OPEN POSSIBILITI<mark>ES</mark>.

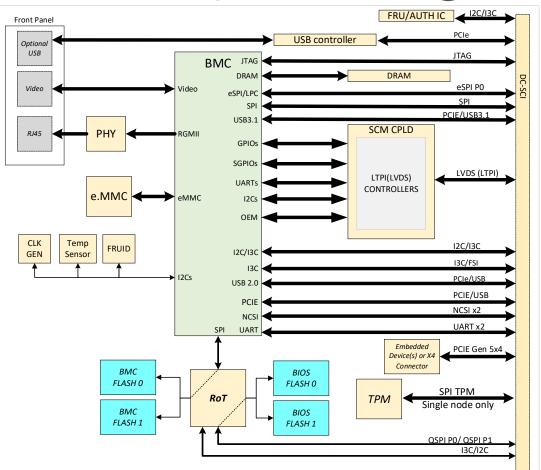

### DC-SCM2.0 example use diagram

PEN

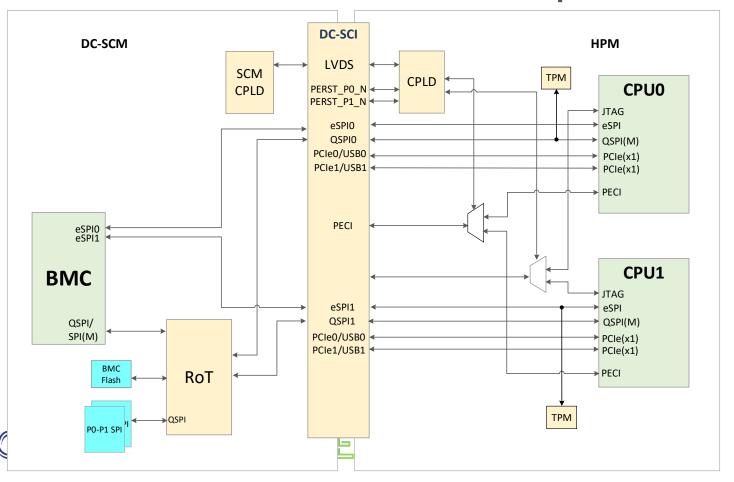

### DC-SCM2.0 dual-node example

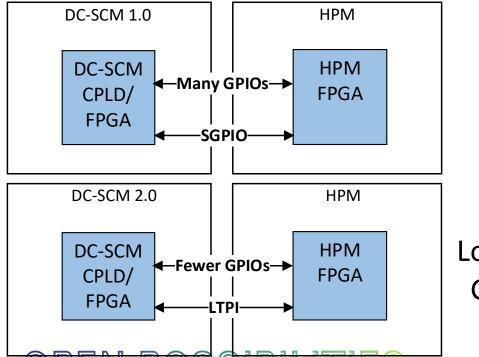

#### DC-SCM2.0 LTPI – LVDS Tunneling Protocol & Interface

Kasper Wszolek and Yi Zeng (Intel) own this section

Slow, Single ended, Fixed length GPIO bit shifter

High Speed, differential, Lower latency, Multi-channel, GPIOs + remote peripherals

CP

See LTPI workshop on-demand video and spec for more details

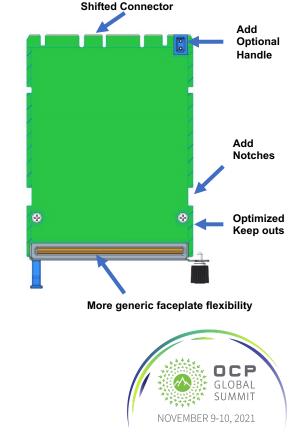

# **DC-SCM2.0** Mechanical Changes

Glen Hanna (Intel) owns this section of the spec Many great ideas from Andrew Junkins (Lenovo)

- All refinements targeted at horizontal form factor only

- Same X-Y board dimensions

- Removed vertical formfactor in the 2.0 spec

- Same 168 pin standard 4C+ connector, shifted to prevent cross version mis-plugs

- Improved keep-outs to maximize usable 3D and board space

- Added eject and install/hold down options

- More generic models for I/O face plate /port flexibility

- Removal of specific daughter card sizes/locations such as TPM and platform root of trust

OPEN POSSIBILITI<mark>ES</mark>.

### DC-SCM2.0 Power Sequencing & Discovery

- "Plug-n-Code" is enabled via "Plug-N-Detect-Else-Halt" Guidance with optional step bypasses in closed / non-cross compatibility necessary environments

- Power state common nomenclatures (Pre-STBY, STBY, S5, S0)

- DC-SCM 2.0 sourced trickle power rail for HPM FRU/ Authentication IC, aiding discovery before engaging system specific rails/interfaces

- Narrowed voltage tolerance to improve DC-SCM peripheral options (from 10-14V to 12.0V +-10% with a new max target wattage)

- Increased battery drain max by 200nA

- Refined physical handshakes and example virtual handshakes

### open possibilit<mark>ies</mark>.

### **DC-SCM2.0 Interface Definition**

- Common bus/signal/partition name & instance nomenclatures

- Best fit pin assignments / bus counts / voltages / mutually-exclusive alternate pin functions for multi-generational expected use cases.

- Accommodates all asks within pin count constraints

- Targeted min BOM cost where possible e.g., 2 clocks vs always a fanout buffer

- Alternate pin functions in typical-to-exotic order

- Defined minimum system power state where bias is allowed for every signal, driving clear rules for cross-power domain logic (avoiding contention + leakage)

- Multi-voltage pin allowances based on DC-SCM 2.0 + HPM combination

- Refined typical example interface drawings to aid adopters

OPEN POSSIBILITIES.

#### High-Level Interface Deltas between 1.0 and 2.0

| Features                       | DC-SCM1.0 | DC-SCM2.0                           |

|--------------------------------|-----------|-------------------------------------|

| SGPIO                          | yes       | removed                             |

| LTPI (serialization over LVDS) | no        | new                                 |

| I2C 3.3V                       | yes       | yes                                 |

| I2C/I3C 1.8V                   |           | new                                 |

| 13C                            | 1.0V      | 1.8V                                |

| I3C/FSI 1.0/1.2                |           | new                                 |

| PCIE topology                  | yes       | Enhanced options                    |

| USB topology                   |           | Host & managed USB enhanced options |

| Dual node support              |           | new                                 |

| SPI                            | yes       | more alt-functions                  |

| NCSI                           | yes       | 2x with alt-functions               |

| VCC_SCM_HPM_FRU                |           | new                                 |

| VIRTUAL_RESEAT                 | yes       | removed                             |

| HPM_FW_RECOVERY                | yes       | removed                             |

| OPEN POSSIBI                   | Lities.   |                                     |

# **DC-SCM Future Exploration Topics**

- New or optional expansion connector for more pins where needed

- Compliance test vehicle

- Continually evaluate evolving interfaces/voltages/HPM use cases

### Call to Action

Project Wiki : <u>https://www.opencompute.org/wiki/Hardware\_Management/Hardware\_Management\_Module</u>

Mailing list: <u>https://ocp-all.groups.io/g/OCP-HWMgt-Module</u>

Call to community to add what is missing/wish-list to public wiki

Specification contribution targeted for 2022

Please visit the Experience Center for LTPI demos

### Thank you!