## THE PATH TO A CHIPLET ECOSYSTEM

0

Ò

Ramune Nagisetty Senior Principal Engineer Director, Process and Product Integration Intel CTO Office

## **LEGAL INFORMATION**

This presentation contains the general insights and opinions of Intel Corporation ("Intel"). The information in this presentation is provided for information only and is not to be relied upon for any other purpose than educational. Statements in this document that refer to Intel's plans and expectations for the quarter, the year, and the future, are forward-looking statements that involve a number of risks and uncertainties. A detailed discussion of the factors that could affect Intel's results and plans is included in Intel's SEC filings, including the annual report on Form 10-K.

Any forecasts of goods and services needed for Intel's operations are provided for discussion purposes only. Intel will have no liability to make any purchase in connection with forecasts published in this document. Intel accepts no duty to update this presentation based on more current information. Intel is not liable for any damages, direct or indirect, consequential or otherwise, that may arise, directly or indirectly, from the use or misuse of the information in this presentation. Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

Copyright © 2019 Intel Corporation.

Intel, the Intel logo, are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others

## **RAPIDLY CHANGING WORKLOADS AND APPLICATIONS**

### Data, AI, and Infrastructure

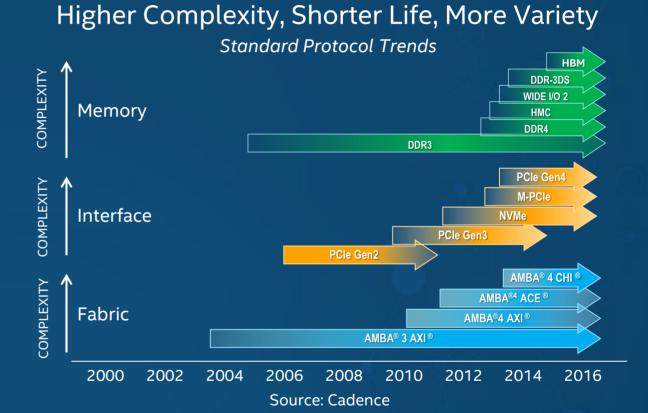

### I/O Variety & Complexity

# Rise of Disruptive Architectures Increasing Bandwidth Requirements ... ARE DRIVING NEW INNOVATION PARADIGMS

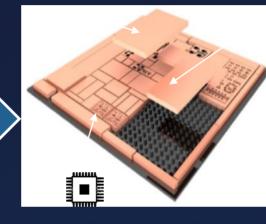

## **PACKAGE IS A PLATFORM FOR INNOVATION & AGILITY**

## **TECHNOLOGY DRIVERS**

(e.g. heterogeneous integration, reticle limited die, IP porting)

## **MARKET REQUIREMENTS**

(e.g. form factor, accelerators, 3<sup>rd</sup> party IP, custom solutions)

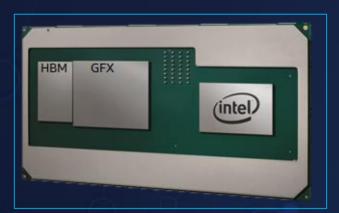

8<sup>th</sup> Gen Intel<sup>®</sup> Core<sup>™</sup> Intel high-performance CPU, HBM2 and AMD\* discrete graphics

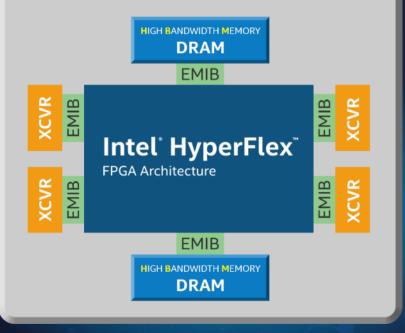

Intel<sup>®</sup> Stratix<sup>®</sup> 10 FPGA HBM + RF XCVR

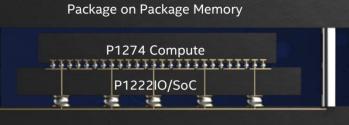

### Intel<sup>®</sup> Lakefield 3D die stacking

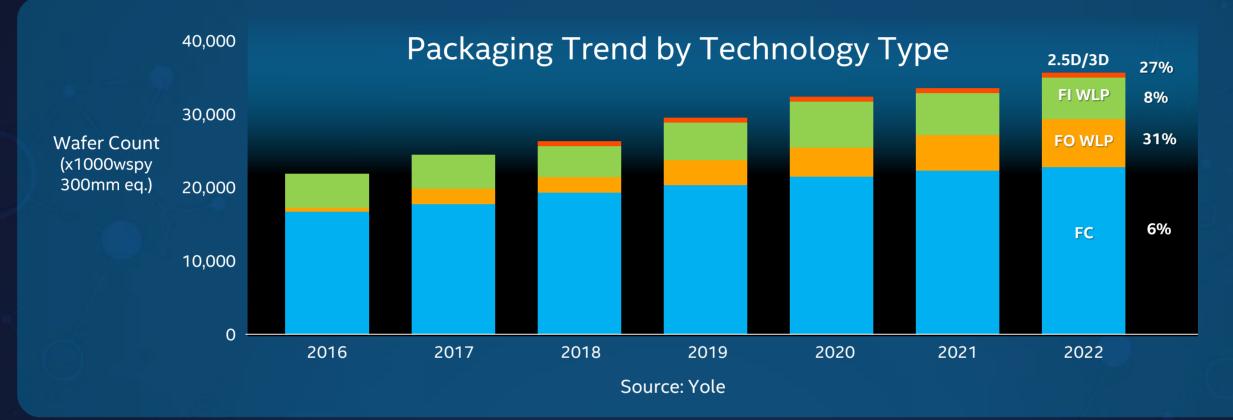

## **PACKAGE-LEVEL INTEGRATION EXPECTED TO GROW FURTHER**

ITRS 2.0 Roadmap Focuses on Heterogeneous Integration and Connectivity

Multivendor Interoperable HBM (High Bandwidth Memory)

27% CAGR in 2.5D/3D Packaging

## Connectivity ory)

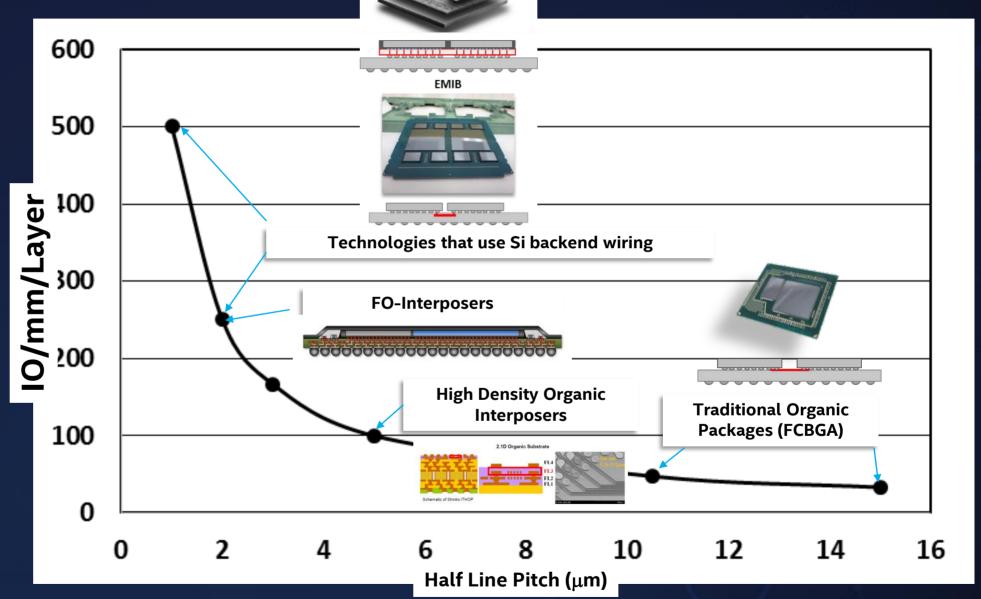

## ADVANCED MCP LANDSCAPE

Si Interposer

- Key Feature Scaling Metrics:

- IO/mm/Layer (Escape Density)

Die Eda

• IO/mm<sup>2</sup> (Die Area)

Technologies with silicon back-end wiring have the highest wire densities

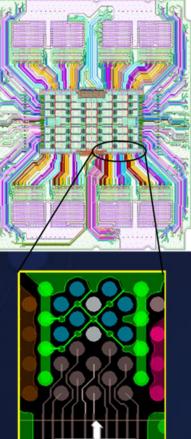

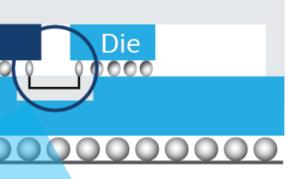

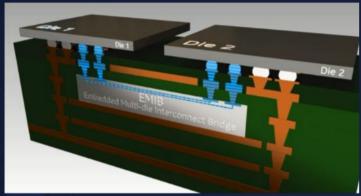

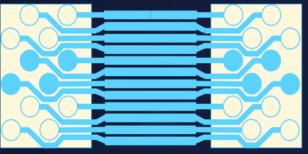

## INTEL® EMBEDDED MULTI-DIE INTERCONNECT BRIDGE (EMIB) Technology

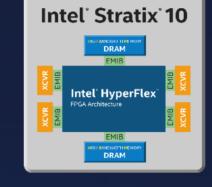

## Intel<sup>°</sup> Stratix<sup>°</sup>10

## Intel® Stratix® 10 FPGAs and SoCs with Intel EMIB Package Lid Die FPGA Die Package Substrate

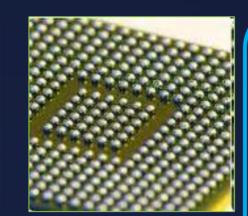

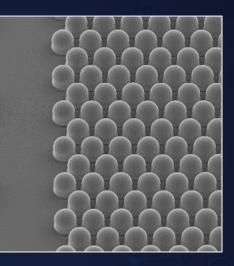

Flip chip bump pitch 100 um

### HBM μ bump pitch 55 um

## 2D/2.5D DENSE MCP TECHNOLOGIES

### **EMIB**

Localized high density wiring No practical limits to die size Standard assembly process Bridge manufacturing much simpler Bridge silicon costs < Silicon interposer No TSVs, Significantly less silicon area

Increased package manufacturing complexity

### **Silicon Interposer**

CTE Matched with Si Excellent chip-attach alignment Pitch scaling

Efforts in place to develop larger than reticle interposers

Interposer size is typically limited by reticle field • TSV capacitance impacts signal integrity of offpackage links Interposer attach adds an extra chip attach step

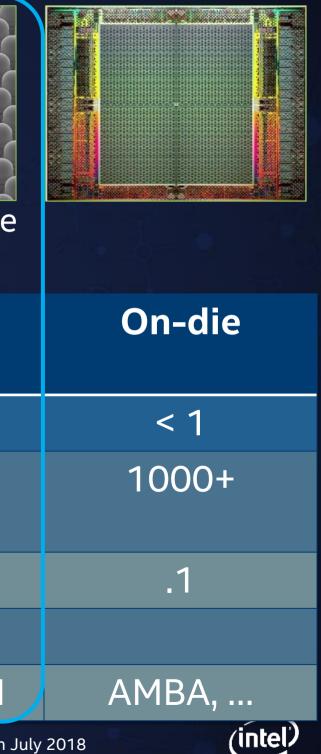

# **NEW PACKAGING STANDARDS**

| 🕿 Near On-Di |

|--------------|

| Capability   |

|                                  | On-board  | On-package<br>(FCxGA) | EMIB      |

|----------------------------------|-----------|-----------------------|-----------|

| Distance (mm)                    | 1000      | 2-50                  | 1-3       |

| Wire Density<br>(lines/mm/layer) | Up to 15  | 35                    | 1000+     |

| Power (pJ/bit)                   | 7-20      | 1-2                   | <1        |

| BW/shoreline (Gbps/mm)           | 200       | 250                   | 1000+     |

| Standards                        | PCIe, DDR |                       | AIB*, HBM |

## **INDUSTRY HAS REACHED AN INFLECTION POINT**

Rapidly Emerging New Workloads & Disruptive Architectures Breakthroughs in Packaging Capabilities Approach On-Die Solutions

New Interface Standards for Package-Level Integration

## WE HAVE AN OPPORTUNITY TO SCALE ECOSYSTEM INNOVATION **THROUGH PACKAGE LEVEL INTEGRATION OF CHIPLETS**

## **DEMONSTRATED RANGE OF CHIPLET SOLUTIONS**

### Kaby Lake G

| Silicon   | Multiple foundries and nodes                                                                                                                                       | Multiple foundries and nodes                                                                                                                                | Internal sili<br>nodes                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Interface | <ul> <li>Industry standard</li> <li>HBM (over EMIB)</li> <li>PCIe (over Std Pckg)</li> </ul>                                                                       | <ul> <li>Industry standard</li> <li>HBM (over EMIB)</li> <li>AIB (over EMIB)</li> </ul>                                                                     | <ul><li>Proprieta</li><li>Logic on l</li></ul>                                            |

| Comments  | <ul> <li>Smaller form factor</li> <li>Best in class IP</li> <li>Same die can be used on board<br/>or in package</li> <li>Most flexible and quickest TTM</li> </ul> | <ul> <li>AIB die2die PHY supports<br/>EMIB &amp; CoWoS</li> <li>FPGA can be configured for<br/>different protocols</li> <li>Mix-n-match approach</li> </ul> | <ul> <li>Top and k<br/>for floor p<br/>thermals</li> <li>Limited in<br/>re-use</li> </ul> |

Package

### Lakefield

### icon on various

ary interfaces logic 3D stacking

### bottom die co-design planning and

nteroperability and

## LEVEL OF INTEGRATION DETERMINED BY CAPABILITIES AND **REQUIREMENTS. ENABLED BY STANDARDS AND BUSINESS MODELS.**

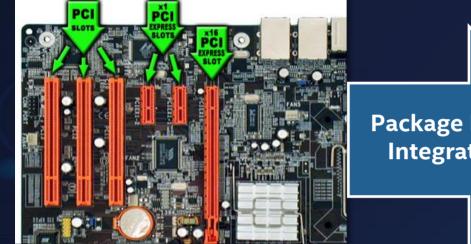

Standardized motherboard interfaces enable the PC ecosystem

**Package Level** Integration

Standardized chiplet interfaces enable a package-level integration ecosystem

SOC Disaggregation

Standardized SOC interfaces (AMBA/AXI) enable foundry ecosystem

### **From Board to Package**

| Benefits   | Smaller form factor<br>Higher bandwidth, lower latency<br>Power efficiency |

|------------|----------------------------------------------------------------------------|

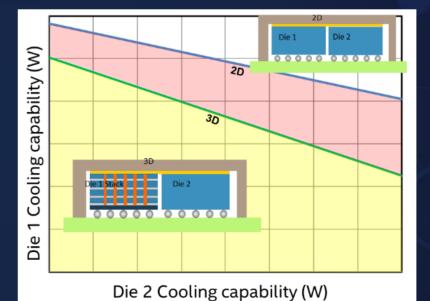

| Challenges | Business models<br>Known good die, cost<br>Thermal limits                  |

| Benefits   | IP portability/suit<br>Potential lower N<br>Address reticle si |

|------------|----------------------------------------------------------------|

| Challenges | Form factor, band<br>Silicon area/powe<br>Manufacturing co     |

### **To Package from SOC**

tability IRE cost & TTM ize limits, yield dwidth, latency,

er overhead

ost

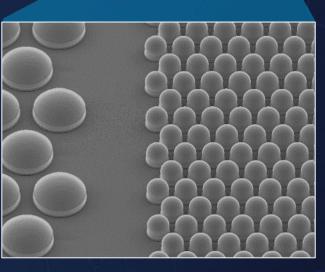

## **TEST AND THERMAL CHALLENGES**

Heterogeneous integration drives the need for true KGD

- Comprehensive content at wafer sort

Extremely challenging to probe fine pitch bumps

- Achieve desired coverage without contacting micro-bumps

- Develop HVM methods for Micro-Bump probe

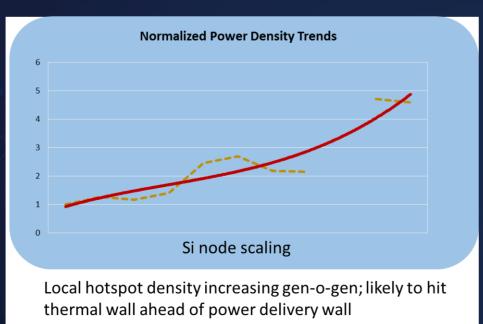

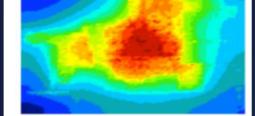

Thermal challenges driven by power, power density, and thermal cross-talk

Need thermal co-design, improved TIMs + power/thermal management

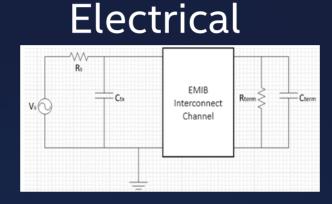

## **CHIPLET INTEROPERABILITY ENABLED BY SPECIFICATIONS AND TOOLS**

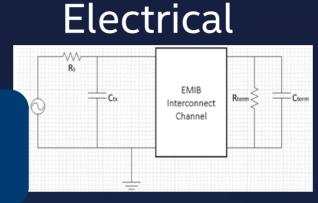

### Mechanical

- Bump and wire sizes

- **Bonding footprint**

- xyz constraints

## Power/Thermal

Power & thermal • modeling and cooling solutions

- Power delivery

- Noise margin •

- Capacitance ٠

|                     | 0ns  10ns  20ns  30                    |

|---------------------|----------------------------------------|

| CLK                 |                                        |

| til_start_v         |                                        |

| til_start_cnt       | $-\sqrt{0}(1)(2)(3)-\sqrt{0}(1)(2)(3)$ |

| til_start_params    | -000001                                |

| til_start_qid       | -(0)(0)(0)(0)(2)(                      |

| eng_til_start_bp[0] |                                        |

| eng_til_start_bp[1] |                                        |

| eng_til_start_bp[2] | /                                      |

- debug, etc.

- Lower productization and NRE cost ullet

- Industry standard test and DFX  $\bullet$

- Functional safety, certification, and traceability •

- Business model and supply chain enablement  $\bullet$

- Easy to use Tools/Flows/Methods

. To minimize area/power/cost and support industry scale interoperability

Data/transaction specifications Management: power, security,

**Configuration & statistics** Manufacturing test access

## **CHIPLET INTEROPERABILITY ENABLED BY SPECIFICATIONS AND TOOLS**

### Mechanical

- Bump and wire sizes

- **Bonding footprint**

- xyz constraints

modeling

Power & thermal • modeling and cooling solutions

- Power delivery

- Noise margin •

- Capacitance ٠

|                     | 0ns  10ns  20ns  3 |

|---------------------|--------------------|

| CLK                 |                    |

| til_start_v         |                    |

| til_start_cnt       | -(0)(1)(2)(3)(0)   |

| til_start_params    | -00000             |

| til_start_qid       | -0/0/0/0           |

| eng_til_start_bp[0] |                    |

| eng_til_start_bp[1] |                    |

| eng_til_start_bp[2] |                    |

|                     |                    |

- debug, etc.

- Lower productization and NRE cost ullet

- Industry standard test and DFX  $\bullet$

- Functional safety, certification, and traceability •

- Business model and supply chain enablement  $\bullet$

- Easy to use Tools/Flows/Methods

. To minimize area/power/cost and support industry scale interoperability

Data/transaction specifications Management: power, security,

**Configuration & statistics** Manufacturing test access

## **CHIPLET INTEROPERABILITY ENABLED BY SPECIFICATIONS AND TOOLS**

### Mechanical

- Bump and wire sizes

- **Bonding footprint** •

- xyz constraints

## Power/Thermal New IEEE 2416

standard for power modeling

Power & thermal • modeling and cooling solutions

- Power delivery

- Noise margin

- Capacitance ٠

reach PHY

- debug, etc.

- Lower productization and NRE cost ullet

- Industry standard test and DFX  $\bullet$

- Functional safety, certification, and traceability •

- Business model and supply chain enablement  $\bullet$

- Easy to use Tools/Flows/Methods

To minimize area/power/cost and support industry scale interoperability

## **Functional**

### New PIPE V5.2 support for configurable short

Data/transaction specifications Management: power, security,

Configuration & statistics

Manufacturing test access

## **POWER MODELING STANDARD IEEE 2416-2019**

IEEE P2416 WG: ARM, Cadence, IBM, Intel, Si2

- Si2 UPM WG: ANSYS, Cadence, Entasys, IBM, Intel, Thrace Systems

- Standardized interoperable system-level power model

- Independent of voltage & temp

- Allows many different levels of abstraction from IP Block > chiplet > SOC/SIP

- Early insight into electro-thermal effects

- Common modeling language targets 3 classes of users

- Model producers: those developing power models

- Model consumers: those using power models to estimate power

- Tool developers: those building EDA power modeling tools

Future: include static/dynamic thermal modeling & process variation

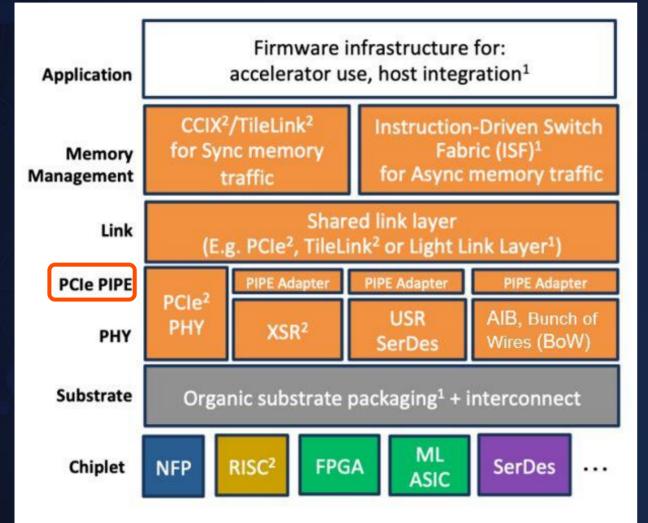

## **PIPE V5.2 SUPPORT FOR SHORT REACH APPLICATIONS**

<sup>1</sup>New Open IP/Specification <sup>2</sup> Existing Open Standard

### Configurable Short Reach PHY (sec 2.6)

- Potentially 50% active power reduction

- Reduce power state transition times & reduce cost by moving from AC coupling to DC coupling

### Carry over board-level ecosystem

- Same Si could be used for both boardlevel & package-level integration

- Mature ecosystems for Si, validation, software, etc.

- Multi-vendor interoperability

- Supports PCIe, CXL, DMI, UPI, CCIX, SATA USB3.x & DisplayPort

# **A DEMONSTRATED RANGE OF INTEGRATION SOLUTIONS** MORE TO BE DONE ON STANDARDS, TOOLS, AND BUSINESS MODELS TO BUILD THE FOUNDATION OF THE EMERGING CHIPLET ECOSYSTEM

PACKAGING IS A PLATFORM FOR INNOVATION, AGILITY, FLEXIBILITY

# **SUMMARY & CONCLUSION**