# OPEN POSSIBILITIES.

# OMI, The Path to High Bandwidth, High Capacity Near Memory

SERVER

...

PERFORMANC

HIGH

NOVEMBER 9-10, 2021

Server Track

# OMI, The Path to High Bandwidth, High Capacity Near Memory

Tom Coughlin, Coughlin Associates, <u>https://tomcoughlin.com</u> Jim Handy, Objective Analysis, <u>https://objective-analysis.com</u>

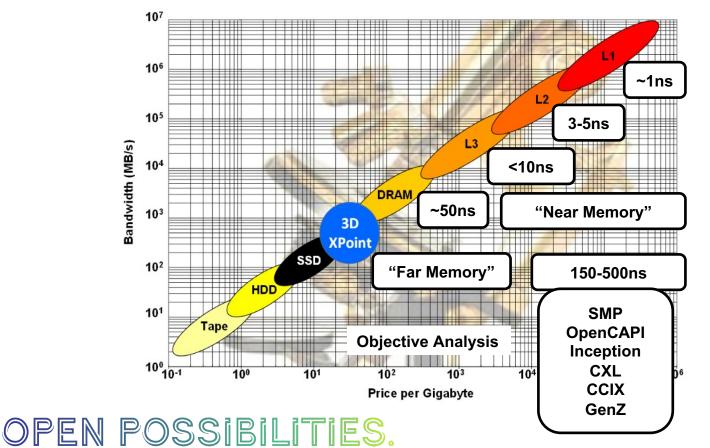

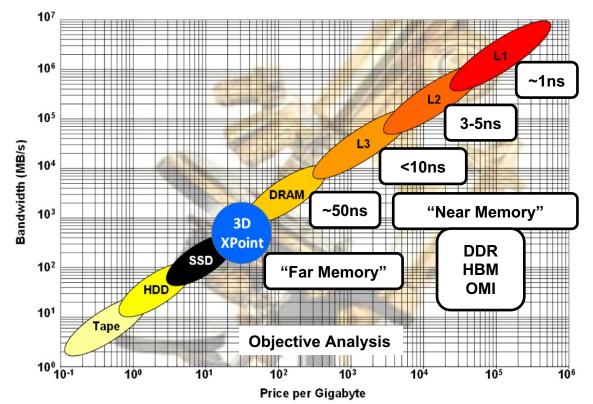

### Preface: Near Memory vs. Far Memory

**SERVER**

HIGH PERFORMANCE COMPUTING

### Preface: Near Memory vs. Far Memory

OPEN POSSIBILITIES.

SERVER

HIGH PERFORMANCE COMPUTING

# Outline

- More Cores Need More Near Memory Bandwidth

- Today's Problems Need Larger and Faster Near Memories

- Three Alternatives DDR, HBM, & OMI

- What Is a DDIMM?

- Supporting a Mix of Near Memories

- Conclusions

OPEN POSSIBILITIES.

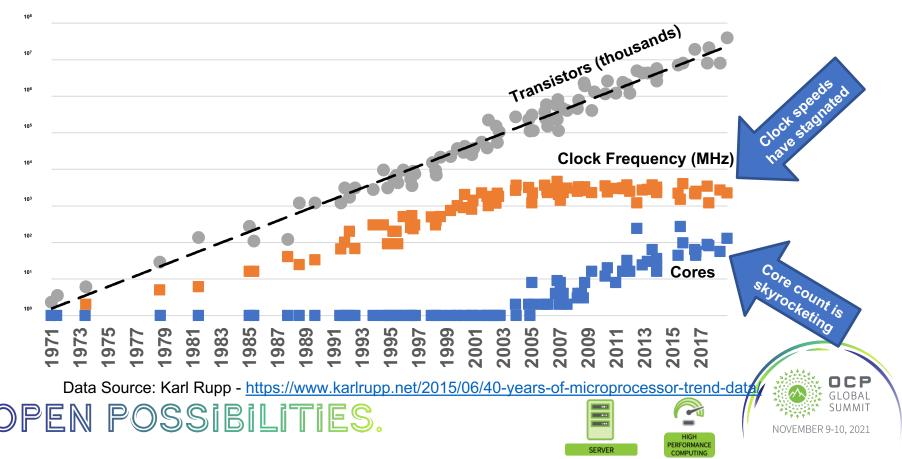

### **Processor Trends Drive Near Memory Demands**

### **Processor Trends Drive Near Memory Demands**

# **Increasing Near Memory Bandwidth**

- Improve the memory interface

- DDR, DDR2, DDR3, DDR4, DDR5

- Increase the bus clock speed

- 1600, 1866, 2133, 2400, 2666, 2933, 3200

- But latency doesn't change as clock speed increases

- Higher clock speeds reduce DIMMs per channel

- Add Memory Channels

#### OPEN POSSIBILITIES.

# More Memory Channels Means More Processor Die Cost & Power

**OPEN POSSIBILITIES.**

Each LRDIMM channel requires 152 processor pins 72 data bits + 18 address bits + 36 strobes + 26 command/other bits 6 Channels = 912 pins 8 Channels = 1,216 pins The most expensive real estate in the system Fast I/O is a power hog Capacitance is the culprit!

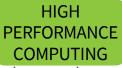

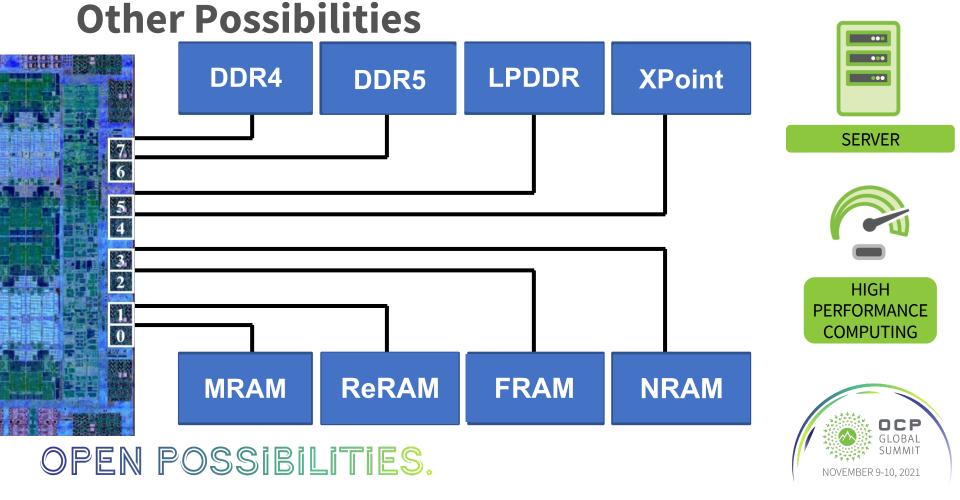

# **Three Near Memory Options**

DDR4 Mainstream & inexpensive HBM2E Costly, but fast 1,000-bit bus! OMI

Introduces SerDes into data path Supports high bandwidth and large memory capacities

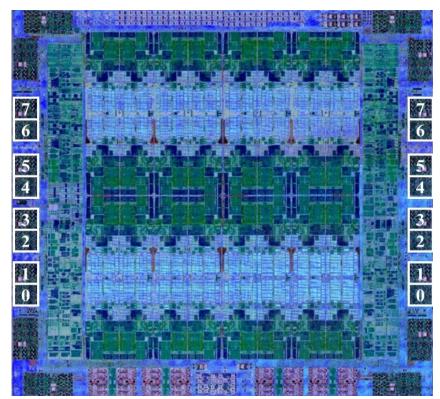

### **OMI & IBM's POWER10 CPU**

**SERVER**

#### OPEN POSSIBILITIES.

#### **POWER10 Stats**

Sixteen OMI channels

256 GB capacity per channel

1TB/s total memory bandwidth (read + write)

64GB/s per OMI channel

2.2mm<sup>2</sup> die area per channel 29.6GB/s/mm<sup>2</sup>

Nearly matches HBM

#### OPEN POSSIBILITIES.

### **OMI DDIMM**

Serial differential signaling ¼ the pins of DDR HBM-like bandwidth

Moves DRAM signaling away from main board, onto DDIMM

Reduces processor's I/O power

Low latency penalty <4ns

Requires a controller

Replaces LRDIMM buffers

Processor no longer tied to one interface (DDR4) or one memory type (DRAM)

30mm<sup>2</sup> die area

Can do on-DIMM processing (ECC, encryption...)

# **Near HBM Bandwidth at >DDR Capacities**

VOVEMBER 9-10, 2021

# Conclusions

Near Memory needs more bandwidth

Near Memory needs larger capacities

More Memory→DDR, Faster Speeds→HBM, Both→OMI

Near-HBM speeds at larger-than-DDR capacities

OMI can support a mix of Near Memory types

# **Call to Action**

Visit the OMI Booth on the OCP Exhibit Floor

Consider adopting OMI as your near memory interface during your next processor design to get a low latency, high bandwidth and high

capacity solution

**OCP GLOBAL SUMMIT 2021**

EXPO FLOORPLAN - BOOTH SELECTION

#### OPEN POSSIBILITIES.

**FNtech**

# References

CXL Consortium, Introduction to Compute Express Link (CXL), 2019 Hot

Interconnects.

Patrick Knebel, et. Al, Gen-Z Chipset for Exascale Fabrics, 2020 Hot Interconnects.

Mazyar Razzaz, DDR Basics, Register Configurations & Pitfalls, Freescale Technology Forum, July 2009.

Low Power Double Data Rate 4 (LPDDR4), JESD209-4D, JEDEC, 6/2021. High Bandwidth Memory (HBM) DRAM, JESD235D, JEDEC, 3/2021.

Karl Rupp - <u>https://www.karlrupp.net/2015/06/40-years-of-microprocessor-trend-</u>data/

https://github.com/karlrupp/microprocessor-trend-data/blob/master/LICENSE.txt

W. Starke and B. Thompto, IBM's POWER10 Processor, 2020 Hot Interconnects.

T. Coughlin and J. Handy, <u>The Future of Low Latency Memory</u>, White Paper, <u>https://Objective-Analysis.com/reports/#Emerging</u>, July 2021.

SAP Standard Application Benchmarks, <u>https://www.sap.com/dmc/exp/2018-benchmark-directory/#/sd</u>

HIGH PERFORMANCE COMPUTING

NOVEMBER 9-10, 2021