# OCP June 25th 2019 CHINA DAY Beijing

# The Co-Evolution of Data Center Hardware and Systems Software

Lintao Zhang | Principle Researcher Microsoft Research Asia

25<sup>th</sup> June, 2019

OCP 2019 CHINA DAY Beijing P June 25th 2019 DAY Beijing

# Introduction

# Many classic systems software are designed decades ago, with many common assumptions:

- CPU is the Central Processing Unit, it is fast, and is getting faster

- Disk is slow, especially for random accesses

- Network is unreliable

- Memory hierarchy is consisted of CPU cache, DRAM, and disk paging.

- Accessing hardware needs to go through OS kernel

- Locality is important, data should be stored close to compute

#### Many of the assumptions are no long true in modern NA data centers

tom's HARDWARE

PRODUCT REVIEWS BUYING GUIDES E3 RASPRERRY PI DE

TRENDING Ryzen 9 3950X Radeon RX 5700

Zen 2 Microarchitecture DDR5 RAM

STORAGE > NEWS

### Boot Your PC at 15GB/s With **Gigabyte's New PCIe 4.0 SSD** Adapter CHINA DAY

by Paul Alcorn May 27, 2019 at 2:42 PM

The debut of AMD's third-gen Ryzen chips hastened the arrival of blazingly-fast PCIe 4.0 SSDs, but we'll soon be jaded about SSDs with a "paltry" 5GB/s of throughput, especially with new models coming with even faster speeds. But what if you could boot your PC with an SSD adapter that hits 15 GB/s?

That's the purpose of Gigabyte's prototype quad-SSD adapter. This

new add-in card snaps into your PCIe slot to get access to the full blazing 64 GB/s of theoretical throughput available through the PCIe 4.0 x16 connection. After you add in the annoying, yet unavoidable overhead of the PCIe interface and RAID. Gigabyte's new prototype has hit up to 15 GB/s when paired with four of the company's new Aorus PCIe 4.0 SSDs. Each of those SSDs hit up to 5GB/s, so the card could potentially push up to 20 GB/s with further tuning.

COMMENTS

O Credit: Tom's Hardware

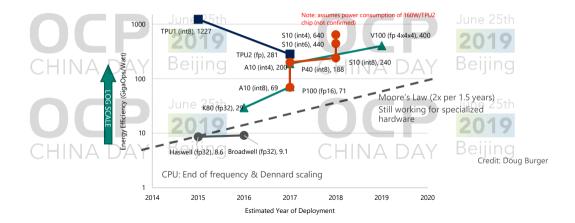

# The rise of domain-specific computing

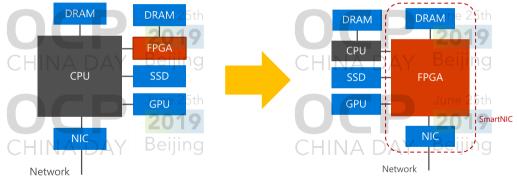

# Cloud Architecture built around Smart NIC

Traditional Thinking

SmartNIC Centric Thinking

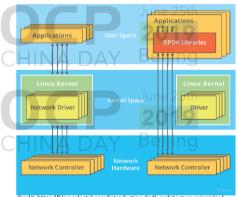

# Kernel can be by-passed for High Speed IO

- Traditional file system calls and hetwork IO are usually in OS kernel **2019**

- May incur too much overheading

RDMA, DPDK and SPDK tries to move data plane to user space and by-pass kernel

But they introduce new APIsijing

Linux Kernel with DPDK

Linux Kernel without DPDK

Credit: https://blog.selectel.com/introduction-dpdk-architecture-principles/

# Agenda

#### 1. Introduction June 25th 2019 OCP 2019 CHINA DAY Beijing 2. Two examples that take advantage of new hardware trends June 25th 3. Going forward and Conclusion OCP June 25th 2019 Beijing June 25th 2019 Beijing CHINA DAY Beijing June 25th 2019 Beijing Beijing CHINA DAY Beijing June 25th 2019 Beijing Beijing June 25th 2019 Beijing Beijing June 25th 2019 Beijing

# Agenda

# Introduction <sup>June 25th</sup> **2019** CHINA DAY Beijing Two examples that take advantage of new hardware trends **2019** Going forward and Conclusion CHINA DAY Beijing

# Example 1: Key-Value Store in Data Centers

Key Value Store is a key piece of systems infrastructure

- Traditionally used as a cache in the cloud

- Now often act as a share data structure

- Example usage: database, graph processing, parameter server,

#### Modern applications require?th

- High throughput

- Clowitail latency AY Beijing

- Write intensive

- Support vector and atomic operations

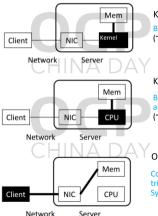

# Key-Value Store Architectures

Kernel TCP/IP 5th Bottleneck: Network stack in OS (~300 Kops per core)

Deijin Karnal Burgas

Kernel Bypass

Bottlenecks: CPU random memory access and KV operation computation (~5 Mops per core)

One-sided RDMA

Communication overhead: multiple roundtrips per KV operation (fetch index, data) Synchronization overhead: write operations

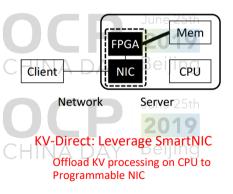

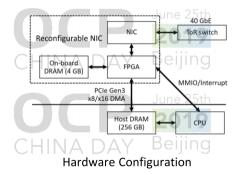

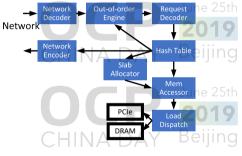

# **KV-Direct Architecture**

**KV Processor**

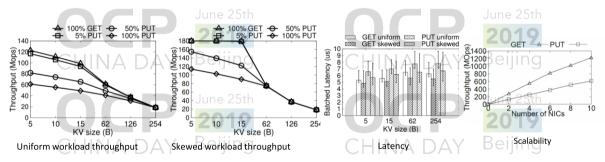

#### **KV-Direct Performance Characteristics**

# KVS Performance Comparison

|    |                     | Tput (Mops)<br>(GET / PUT) | Power<br>(Kops/W)            | Architecture        | Latency (us)<br>(GET / PUT) | June 25th |

|----|---------------------|----------------------------|------------------------------|---------------------|-----------------------------|-----------|

|    | Memcached           | 1.5 / 1.5                  | 5 / 5                        | TCP/IP              | 50 / 50                     |           |

|    | MemC3               | 4.3 / 4.3                  | 14 / 14                      | TCP/IP              | 50 / 50                     | 2019      |

| СН | RAMCloud            | 6/Beiiind                  | 20 / 3.3                     | Kernel bypass       | 5/14                        | Beijing   |

|    | MICA (12 NICs)      | 137 / 135                  | 342 / 337                    | Kernel bypass       | 81/81                       | June 25th |

|    | FARM                | 6/3                        | 30 (261) / 15                | One-side RDMA       | 4.5 / 10                    |           |

|    | DrTM-KV             | 115/14 25th                | 500 (3972) / 60              | One-side RDMA       | 3.4 / 6.3                   |           |

|    | HERD                | 35/25 9                    | 490 / 300                    | Two-side RDMA       | 4/4                         | 2019      |

|    | FPGA-Xilinx         | 14/14                      | 106 / 106                    | Standalone FPGA     | 3.5 / 4.5                   | Beijing   |

|    | Mega-KV DAY         | 166 / 80                   | 330 / 160                    | GPU CHIN            | 280 / 280                   | Deijing   |

|    | KV-Direct (1 NIC)   | 180 / 114                  | 1487 (5454) /<br>942 (3454)  | Programmable<br>NIC | 4.3 / 5.4                   |           |

|    | KV-Direct (10 NICs) | 1220 / 610                 | 3417 (4518) /<br>1708 (2259) | Programmable<br>NIC | 4.3 / 5.4                   |           |

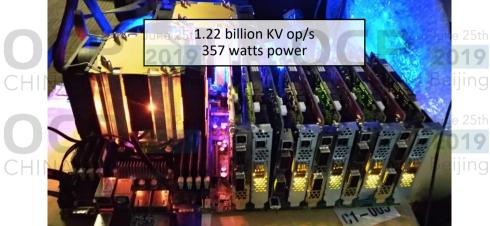

# New Milestone for KVS Performance

# Takeaway for KV-Direct

• This is an emerging paradigm change in data center

# Example 2: Socket for Communication

#### Socket wastes CPU Socket is the universal communication primitive Guest Kernel Time 📋 🗖 Application Time Designed half a century ago NSC DNS SERVER REDIS KEY-VALUE STORE Complicated semantic NGINX LOAD BALANCER Low performance, high overhead IGHTTPD HTTP SERVER 22% Socket wastes low latency DC Challenges: network How to be fully compatible with native socket How to leverage modern hardware such as RDMA and multicore. How to maintain isolation and security

Cumulative Overheads

Interrupt

TCP

Source: Luiz Barroso, Mike Marty, David Patterson, Parthasarathy Ranganathan.

Attack of the Killer Microseconds, Communications of the ACM, April 2017

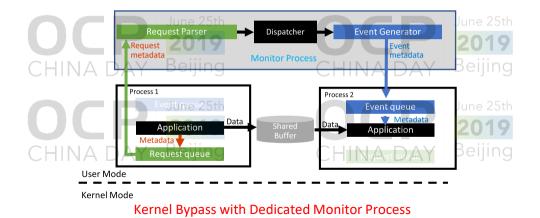

# SocksDirect: Fast and Compatible User Space Socket

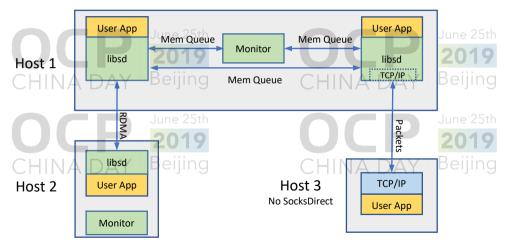

# SocksDirect Supports Different Transports for Data

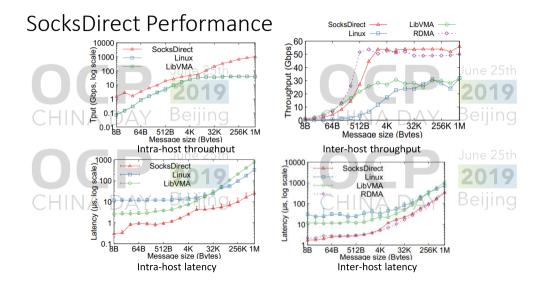

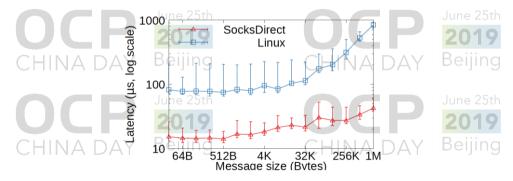

## Application End-to-End Performance with SocksDirect

Nginx HTTP End-to-End Latency

# Takeaway for SocksDirect

SocksDirect implements a high-performance Socket system in user space 25th

2019

- Bypass OS kernel to reduce overhead

- Dedicates a core for monitor process (take advantage of multi-core CPU)

- Can act as a drop-in replacement for classic socket without app modification

- Achieve orders of magnitude performance improvements

- Published in SIGCOMM19he 25th 2019 Other traditional OS surtants functions can be improved in a similar man

Other traditional OS systems functions can be improved in a similar manner.

# How is this related to OCP

#### Microsoft is contributing hardware innovations

- SmartNIC: FPGA enabled programable NIC

- Zipline : Compression Engine based on FPGA

- Cerberus: Hardware root of trust Denali: Cloud optimized Flash storage

#### New hardware in Data Centers require us to rethink systems software design

- Which abstraction to use for non-volatile Storage Class Memory?

- Will CPU be relegated to become a second-class citizen in data center?

- How can we evolve the systems abstraction while keep software modification to a minimum?

Hardware/and Systems software heeds to evolve together A DAY

We demonstrate two cases that can greatly improve systems performance by taking advantage of new hardware

# OCP June 25th 2019 CHINA DAY Beijing OCP 2019 CHINA DAY Beijing CHINA DAY Beijing CHINA DAY Beijing CHINA DAY Beijing

CHINA DAY Beijing

OCP 2019 CHINA DAY Beijing OCP June 25th 2019 CHINA DAY Beijing