## OCP - ODSA Project

Commercialization Use Case

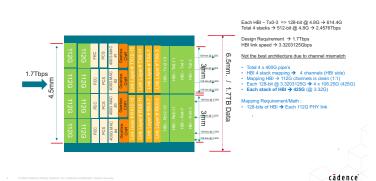

cadence

**UltraLink D2D PHY & OHBI**

Rishi Chugh

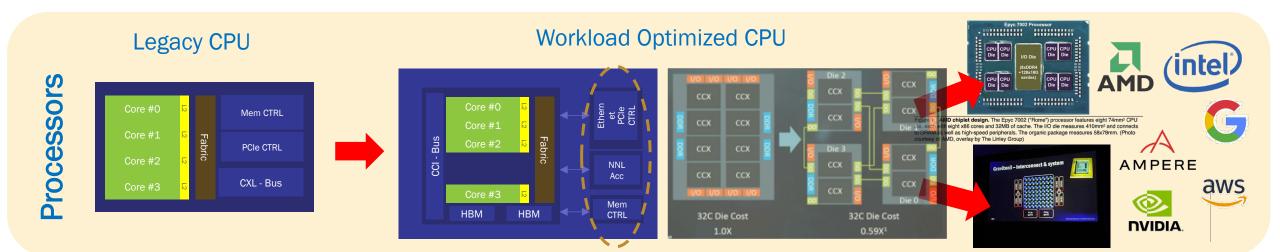

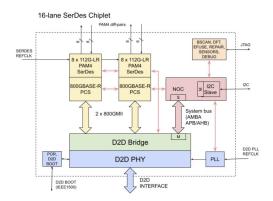

## Chiplet Examples for Heterogenous System Design

- New Design paradigm, from IP reuse to Chiplet reuse

- Primary drivers for chiplet functionality:

- Multi-Core

- GPGPU

- CPU + Workload accelerator

- Scientific computing

- **Processor**

- Mem

Controller Die

64 ↑ ARM

Neoverse v1

Core

Mem

Controller Die

PCIe Controller

Die

PCIe Controller

Die

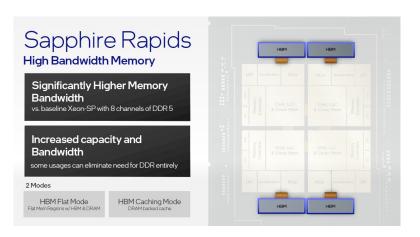

- HBM Cache Extensions

- PIM (Processing In Memory)

- Packet Buffering / Look Ups

- Data Analytics / Cache Ext

**Memory / Storage**

- Host / Client / IO Peripherals

- NoC (Chip / Interposer)

- Server SoC (CPU+Chipsets)

- WEB servers , Fabric , NIC

CONNECTIVITY

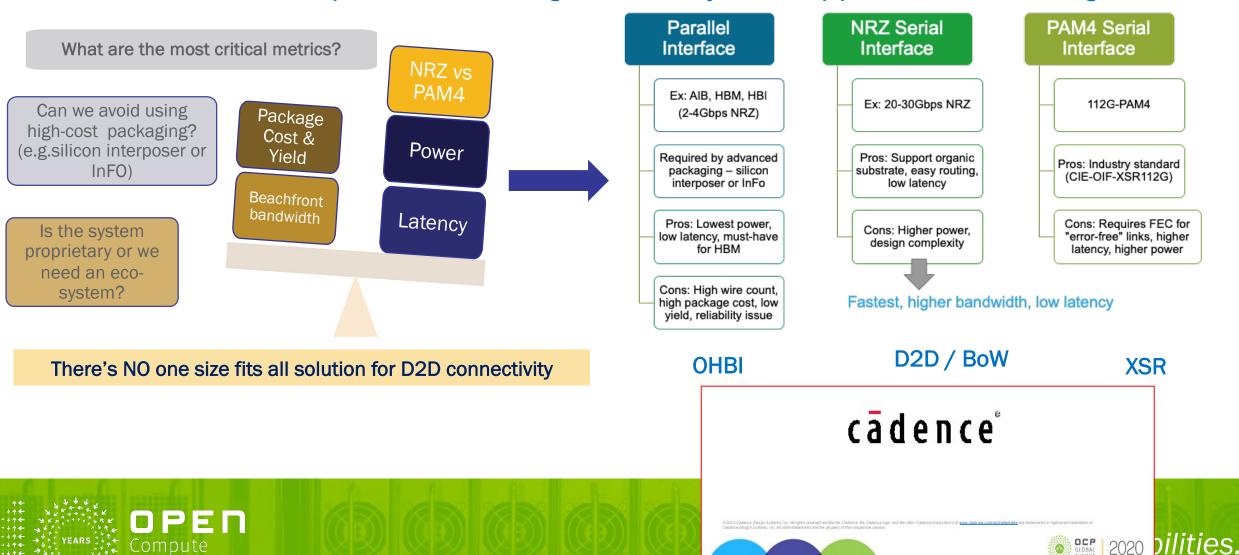

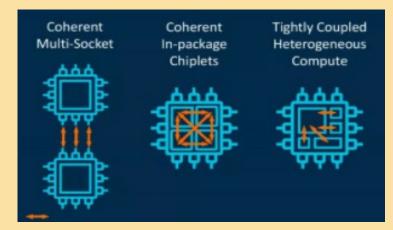

## High Speed Connectivity & Chiplets Strategy

Investment for Chiplet based design driven by SoC Application & Scaling

Project

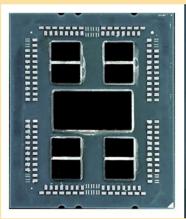

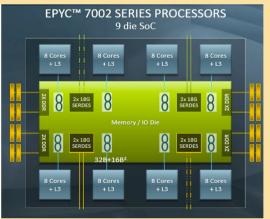

### Chiplet Landscape (OEM, Close Box, High Barrier To Entry)

## Chiplet Landscape (CDNS has all these IP + System know how)

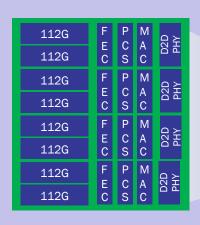

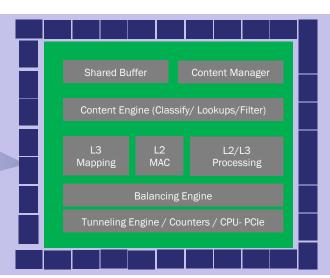

- LO/L1 layer implemented on the chiplet

- Provides optimal fabric design flexibility

- scalability, larger buffer for high bandwidth

- i.e. 25T+ on monolithic die

- Can be potentially extended to enable

GB , FEX & Multi-Channel features on the chiplet

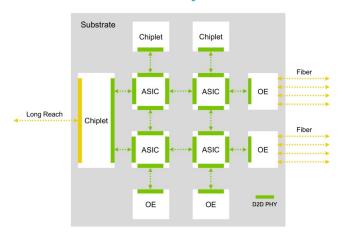

#### **Block Diagram**

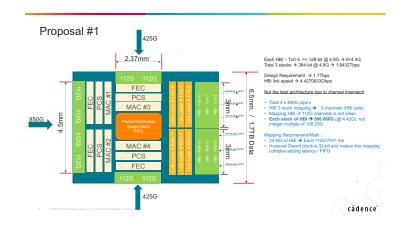

#### Proposal #2B

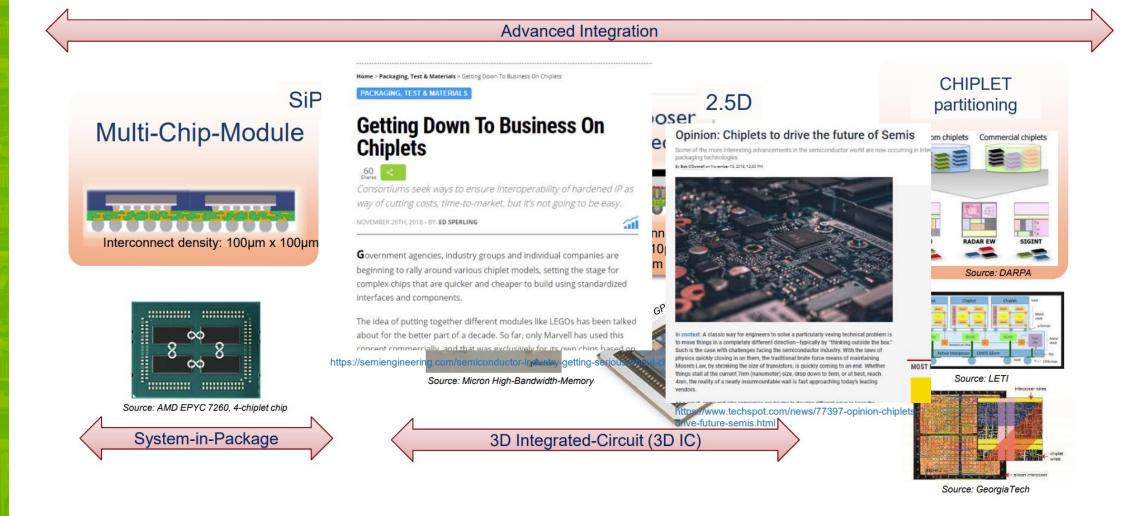

## SoC-Advance Package Integration To Chiplet Partitioning

## Cadence / ODSA

- Cadence contributing and carving industry path towards chiplet based SoC design

- Full 3D tool support working on close partnership with OCP as well as leading multiple foundry house

- Successful commercial deployments of chiplet based SoC architectures

- Closely contributing, following and enabling industry on BoW & OHBI standards

- Existing UltraLink offering similar to BoW architecture

- OHBI under development for industry enablement

## Comparison: Technical Specifications

| Metrics                                         | Die-to-Die                                                        | 112G-XSR                                             | HBI* v1.1                                    |

|-------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------|

| Line Rate                                       | 20-40Gbps                                                         | 112Gbps                                              | 16Gbps                                       |

| Number of wires in a macro                      | 6 Rx or Tx                                                        | Up to 8                                              | 64 to 1024 bits                              |

| Max Beachfront Bandwidth (Gbps/mm) (single row) | 500 Gbps/mm                                                       | 500 Gbps/mm                                          | >4 Tbps/mm (Tx + Rx aggregated)              |

| Insertion Loss @ Nyquist                        | 8db @ 20GHz                                                       | 10db @ 28GHz                                         | <3db @ 16GHz                                 |

| Signaling                                       | Single Ended, NRZ                                                 | Differential, PAM4                                   | Single Ended Data, Differential Strobe       |

| Power (pj/bit)                                  | 1.5pJ/bit                                                         | 1.87pJ/bit                                           | 0.5pJ/bit                                    |

| Lane Area (one TX+RX)                           | 0.67mm <sup>2</sup> (240G Rx + 240G<br>Tx, half duplex)           | 0.31mm² (112G Rx + 112G Tx, full duplex)             | 0.168mm² (512G Rx + 512G Tx, half duplex     |

| Area/Tbps                                       | 2.8 mm <sup>2</sup> /Tbps                                         | 2.76 mm <sup>2</sup> /Tbps                           | 0.22 mm <sup>2</sup> /Tbps                   |

| Clocking                                        | Forwarded Clock                                                   | Independent clock (CDR)                              | Forwarded Clock Strobe                       |

| PMA Latency                                     | 5.4ns (Rx+Tx @ 40Gbps)                                            | 8.4ns (Rx+Tx @ 112Gbps)                              | <5 ns Tx "DFI"->Pad<br><5 ns Rx Pad -> "DFI" |

| Per Bit Alignment                               | Per bit Phase adjustment                                          | CDR                                                  | Per bit Phase adjustment                     |

| Raw BER                                         | 1e-15, no-FEC                                                     | 1e-9 (pre-FEC)                                       | 1e-15 (pre-ECC/FEC)                          |

| Process                                         | 7nm & 5nm                                                         | 7nm                                                  | N3                                           |

| Bump pitch                                      | 130u                                                              | 130u                                                 | 40.3/40/70um (diag/X/2Y)                     |

| Other                                           | Line Rate flexible for optimal<br>Performance & Power<br>tradeoff | Compatible with Standard Ethernet PMA (OIF-112G-XSR) | 0.3V IO                                      |

# cadence®