# Cost-Aware Exploration for Chiplet-Based Architecture with Advanced Packaging Technologies

<u>**Tianqi Tanq**</u>, Yuan Xie <u>**tianqi tang@ucsb.edu**</u>, <u>yuanxie@ece.ucsb.edu</u> University of California, Santa Barbara

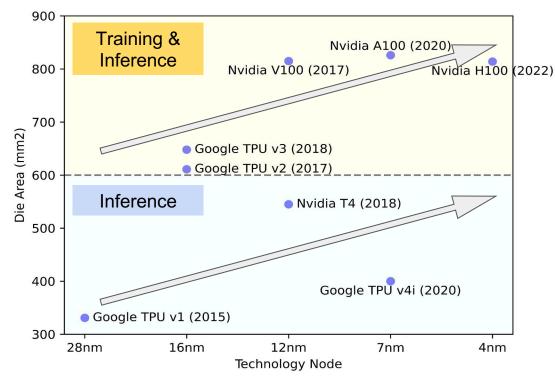

#### Motivation (1/3): Trends of ML Accelerators in Datacenter

- Tech Node scales down while Silicon Area gets larger.

- From Cost Perspective, Monolithic vs Chiplet <sup>(9)</sup>

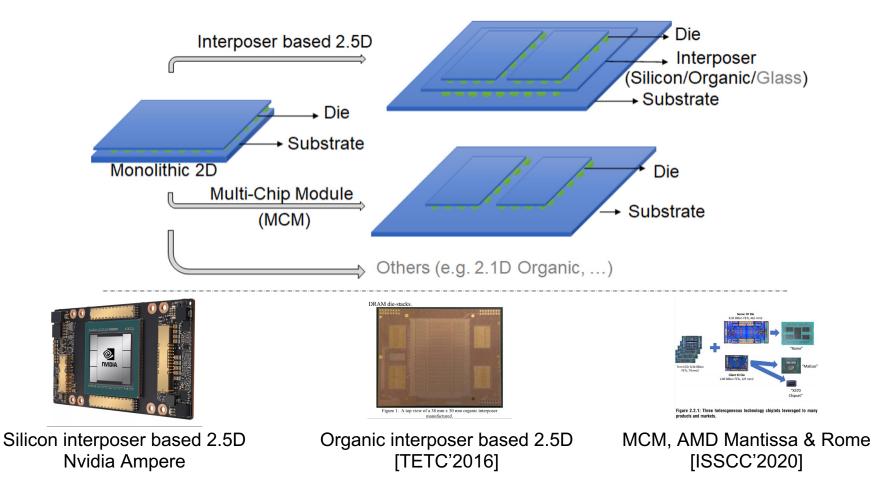

## Motivation (2/3): The Advanced Package Technologies

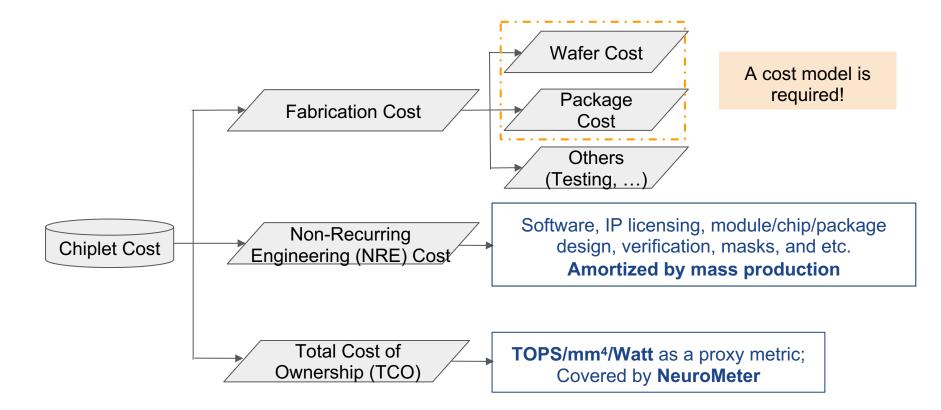

#### Motivation(3/3): Cost Model of Chiplet System

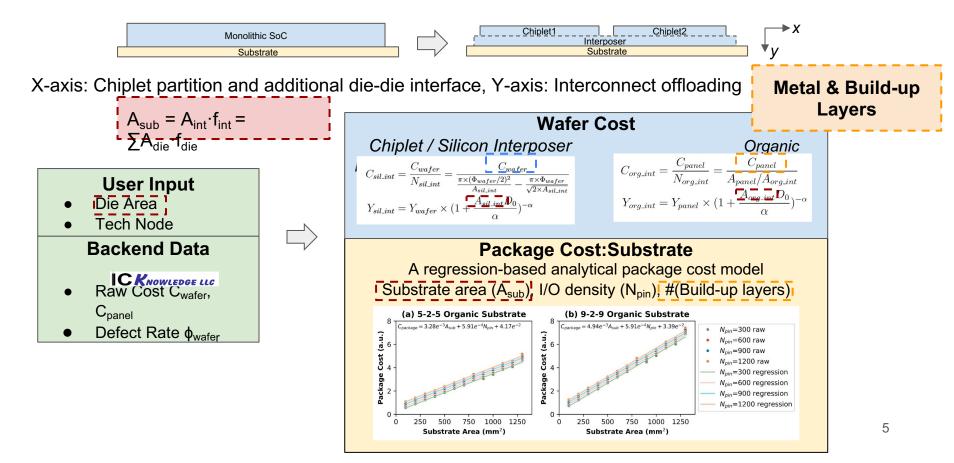

#### Manufacture Cost Modeling for Chiplet-based Architecture

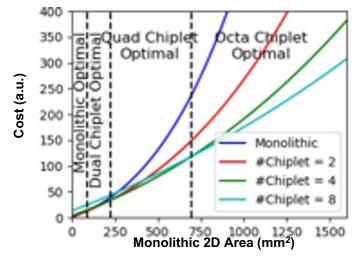

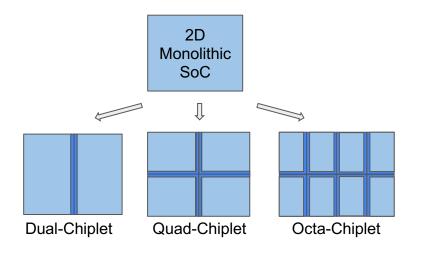

# Case Study (1/2): Homogeneous Chiplet System

• The optimal partition granularity

Observation:

- Fine-grained partition (or larger #Chiplet) does not always win in terms of cost.

- Under the optimal granularity, *Area\_per\_chiplet* falls in the range of 100mm<sup>2</sup> to 200mm<sup>2</sup>.

- MCM system can also get satisfying cost benefits, but silicon interposer CANNOT.

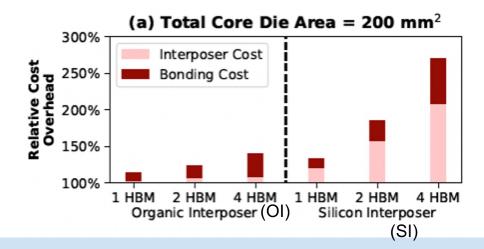

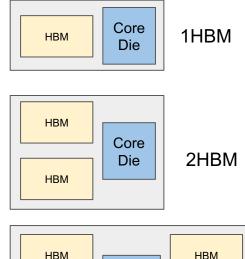

## Case Study (2/2): Heterogeneous Chiplet System

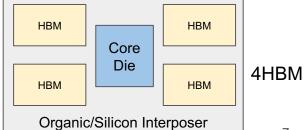

• Heterogeneous Chiplet System with HBM Stacks

Observation:

- OI introduces less than 50% overhead for HBM stacks; while SI gets much larger cost overhead;

- The bonding cost takes the majority in OI; while the interposer cost takes the majority in SI.

## Summary

- Cost Model for Chiplet System with Advanced Package Technologies:

- Supporting the cost of silicon/organic interposer based 2.5D and MCM

- Cost-aware study on the homogeneous/heterogeneous chiplet systems

# **Thanks for Your Attention!**

Q&A