## ACCELERATING INNOVATION THROUGH CHIPLETS OCP/ODSA WORKSHOP

6/10/2019 David C. Kehlet, Research Scientist

## Legal Information

This presentation contains the general insights and opinions of Intel Corporation ("Intel"). The information in this presentation is provided for information only and is not to be relied upon for any other purpose than educational. Statements in this document that refer to Intel's plans and expectations for the quarter, the year, and the future, are forward-looking statements that involve a number of risks and uncertainties. A detailed discussion of the factors that could affect Intel's results and plans is included in Intel's SEC filings, including the annual report on Form 10-K.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at www.intel.com.

Results have been estimated or simulated using internal Intel analysis or architecture simulation or modeling, and provided to you for informational purposes. Any differences in your system hardware, software or configuration may affect your actual performance.

<sup>†</sup>Tests measure performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit www.intel.com/benchmarks.

Copyright © 2019 Intel Corporation.

Intel, the Intel logo, the Intel. Experience What's Inside logo, eASIC, and Stratix are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others

### The Case for Chiplets

"It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected." <sup>1</sup>

Gordon E. Moore

<sup>1</sup>3rd Page of Moore's 1965 paper, "Cramming more components onto integrated circuits"

## Why are Chiplets Now Interesting?

Heterogeneous Integration advantages (you can mix processes) → Not New

Time-to-market advantages (no need to port everything to a new node) → Not New

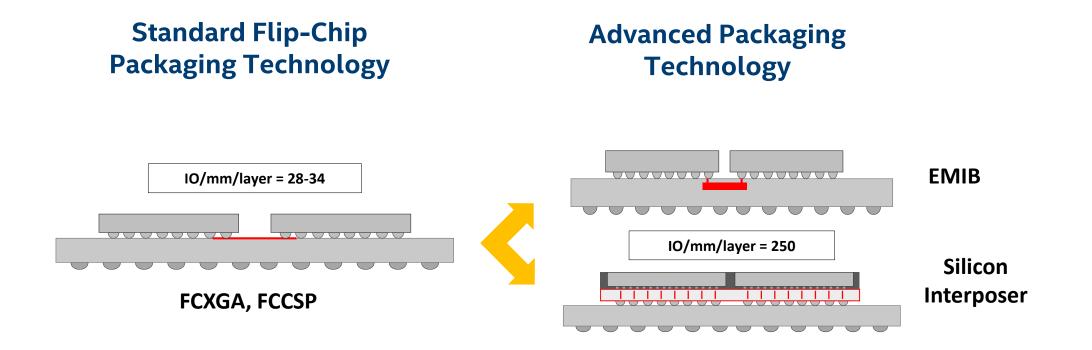

Advanced Packaging Technology → New!

(intel

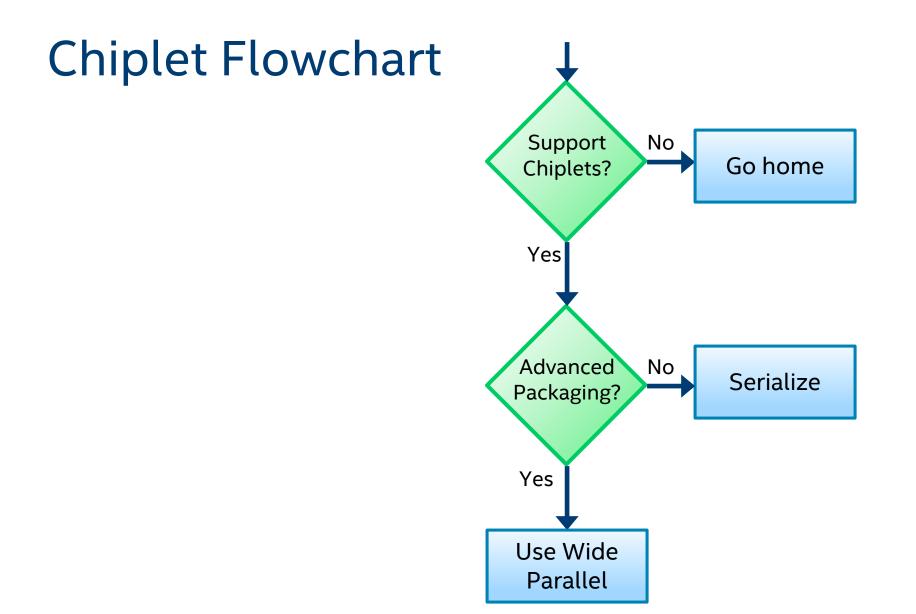

## Packaging Technology

Advanced packaging technology provides 7-8x IO density increase

## When Wires Are Free

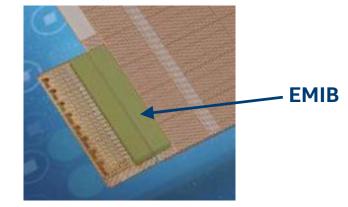

Silicon Bridge or Interposer

- 500 wires/mm → 4,000 wires in Intel<sup>®</sup> Stratix<sup>®</sup> 10 FPGA EMIB

- Typical interposer  $\rightarrow$  USD 0.0005 per wire

- Conclusion: spend very little at each end of the wire

- Don't spend silicon on serialization, complex SERDES, encoding schemes, I/O training, pre-emphasis or equalization

- More Gbps/wire is not better when you can go wider

Google's FASTER Trans-Pacific Cable (2016)

- 6 fiber pairs: 12 "wires"

- Cable cost USD 300M → USD 25M per wire

- Conclusion?

- Spend everything you can at each end of the wire!

Image Source: US Navy

5 trillion times more!<sup>†</sup>

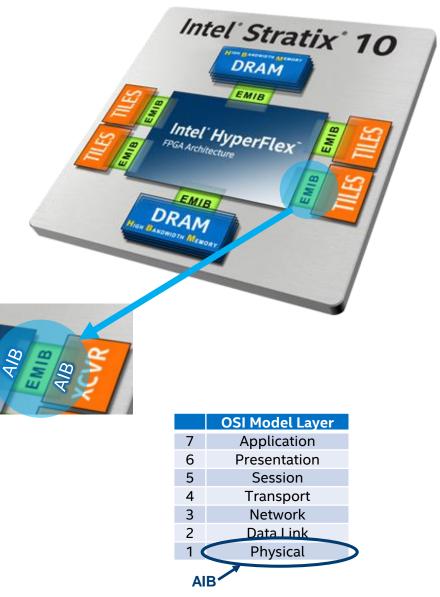

## AIB Die-to-Die Physical Interface

**AIB:** Common chiplet physical interface

- Advanced Interface Bus (AIB)

- AIB is a clock-forwarded parallel data transfer like DDR DRAM

- Advanced Packaging with a 2.5D interposer like CoWoS, or EMIB

- AIB is PHY level: OSI Layer 1

- Build protocols like AXI\*-4 or PCI Express\* on top of AIB

inte

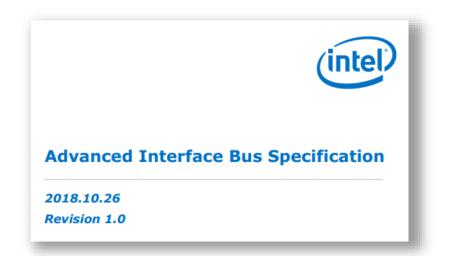

## **AIB Public Releases**

#### **AIB Specification Released October 2018**

#### **AIB Public Specification includes:**

- Electrical specs, bump array mechanicals, data/clock/ control signal definitions, reset handshaking, JTAG reqts

- Available at <u>https://github.com/intel/aib-phy-hardware/tree/master/docs</u>

| intel/aib-phy-hardware                                                              | ×                                                                      | +              |               |             |             |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------|---------------|-------------|-------------|

| ← → C ☆ ⓐ GitHub, Inc. [US]   https://github.com/intel/aib-phy-hardware             |                                                                        |                |               |             |             |

| Search or jump                                                                      | to                                                                     | 1              | Pull requests | Issues      | Marketplace |

| I intel / aib-phy-hardware                                                          |                                                                        |                |               |             |             |

| ♦ Code (!) Issue                                                                    | s 🚺 🕺 🏦 Pi                                                             | ull requests 0 | Projects 0    | 🔳 Wiki      | Insights    |

| No description, website, or topics provided.                                        |                                                                        |                |               |             |             |

| 😯 8 commits 🔋 1 branch                                                              |                                                                        |                |               | > 0 release | 25          |

| Branch: master ▼ Ne                                                                 | w pull request                                                         |                |               |             | Crea        |

| 🐺 xinyang2k added sim_dcc example test under how2use directory. It demonstrate ho 🗔 |                                                                        |                |               |             |             |

| 🖿 aib_lib                                                                           | added two new files: aib_lib/c3dfx/rtl/tap/dbg_test_defines.v and dbg  |                |               |             |             |

| docs                                                                                | Add files via upload                                                   |                |               |             |             |

| 🖿 how2use                                                                           | added sim_dcc example test under how2use directory. It demonstrate ho. |                |               |             |             |

| ndsimslv                                                                            | Initial comr                                                           | mit            |               |             |             |

|                                                                                     |                                                                        |                |               |             |             |

| 🛅 rtl                                                                               | Initial comr                                                           | mit            |               |             |             |

| LICENSE                                                                             | Initial comr                                                           |                |               |             |             |

#### AIB Open Source Released January 2019

#### **AIB Open Source on GitHub**

- Register transfer level (RTL), netlists, generic cell library

- Available at <u>https://github.com/intel/aib-phy-hardware</u>

- Purpose: reduce development cost

## **Designing for Heterogeneous Integration: Interfaces**

How to enable design for Heterogeneous Integration?

- 1. Reduce silicon development cost

- Make die-to-die interface IP in your silicon technology as close to free as possible

- AIB Spec and AIB logic design already released (see GitHub)

- Open source AIB physical design research is in progress

- 2. Expand access to advanced high-density packaging (next page)

## **Designing for Heterogeneous Integration: Interposers**

Example of Interposer Design Enablement: BroadPak

#### BROADPAK ENABLING CHIPLET INTEGRATION

#### BroadPak is a 2.5D/3D integrator

Over 11 years experience in 2.5D/3D design, manufacturing and SIP assembly

#### Design/manufacturing Services

- Silicon interposer/organic substrate Co-design, Signal/power/thermal integrity

- Silicon interposer/organic substrate manufacturing (no strings attached)

- Advanced assembly

#### Chiplet Management (upcoming)

Work with IP provider to maintain inventory of their IP Chiplet

#### Support

Provide guidance and support to IP providers

#### Book/workshops

- To help newcomers and practicing professionals learn the foundations of Heterogeneous design

- Within 1 year, over 150 universities worldwide acquired BroadPak Book: Foundations of Heterogeneous Integration: An Industry-Based, 2.5D/3D Pathfinding and Co-Design Approach

From Farhang Yazdani, President and CTO of BroadPak

Farhang Yazdani

Foundations of

Heterogeneous

Integration: An

Pathfinding and

Co-Design Approach

Industry-Based, 2.5D/3D

Springer

## Data Rate

#### AIB 1.0 is 2Gbps/wire today. Why not more Gbps/wire now?

Clearly will be possible

112 Gbps XSR SERDES, GDDR6-like 16 Gbps/wire, others with unique signaling technology

Questions to ask:

- Cost

- How much does it cost to build or license IP in your silicon process?

- How much silicon area does the interface really use? (PLL, voltage regulators, independent supplies, serializers, encoders)

- Complexity

- How do you interface your 500 MHz 1 GHz core chiplet logic to the intellectual property (IP)?

- How much latency from your core to the other chiplet's core?

- How do you control training and link states?

- Why does multi-die heterogenous integration make sense now, when it didn't make sense before?

- Answer: Advanced high-density packaging is enabling technology!

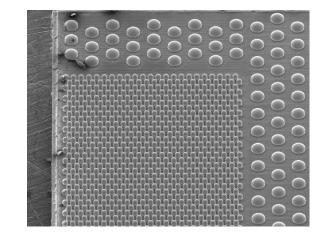

## **AIB Technology Drivers**

Microbump spacing

- 55u is in production

- 35u would provide a nice doubling of density!

#### I/O voltage

- Lower voltage would drive lower energy per bit

- Compatibility with current AIB 0.9V I/O chiplets is very important

#### Line rate

- Very high-bandwidth applications such as direct RF sampling analog-to-digital converters (ADCs) or digital-to-analog converters (DACs) will continue to push higher bandwidth

- Doubling the data rate is feasible, watch latency

Microbump spacing + I/O voltage + line rate  $\rightarrow$  AIB 2.0

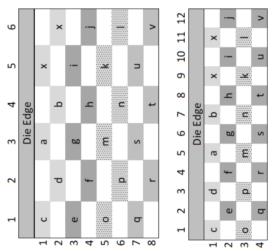

#### Intel® Stratix® 10 FPGA 55u microbump array

55u to 35u microbump assignment for straight-line routing compatibility

# PROTOCOLS ON DIE-TO-DIE INTERFACES

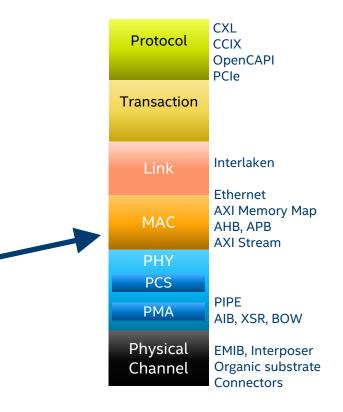

## Interconnect Stack

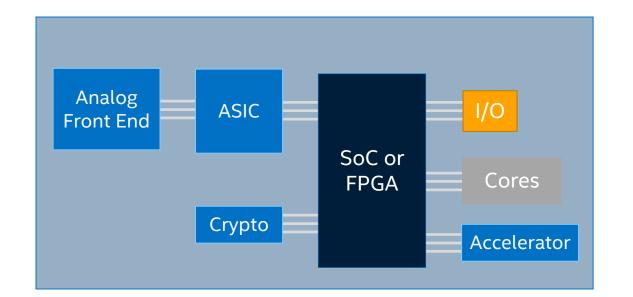

- CPU Accelerator Use Cases

- Software needs a coherent view of host and device attached memory

#### → Today these accelerators are often PCI Express cards

Memory Mapped and Streaming Protocol Use Cases

#### → These often come from die disaggregation (would build monolithically if it were easy)

- Network data (SERDES, MAC)

- Raw or processed live sensor data

- Control and status registers

- Configuration, firmware loading

- Memory controllers

**Example Stack Components** CXL Security Protocol CCIX Addressing OpenCAPI Translation PCle Transaction Arbitration Packetization Flow Control Interlaken Error Notification/Retry Link Frame Sync Ethernet Training **AXI Memory Map** De-skew MAC AHB, APB Scrambling AXI Stream PHY **Power Sequencing** PCS Voltage Swing PIPE **Analog Buffers** PMA AIB, XSR, BOW **Device Shoreline XY** Physical EMIB, Interposer Clocks, Signal assignment Organic substrate Channel Bump Map, Power/Ground Connectors

## Protocols On Die-to-Die Interfaces

Die-to-Die products need a variety of protocols to meet product goals

- ASIC developers like their AXI\*-style lightweight protocols

- Software developers want a coherent memory model

- $\rightarrow$  One protocol will not meet all use cases and applications

Two camps?

- Large scale integration (currently PCIe boards)

- CXL\*, CCIX\*, OpenCAPI\*

- Common point at the PIPE layer: build a PIPE shim on your PHY

- Consortia already in place here

- Monolithic-like (on die module-to-module) developers

- AXI\* Streaming, AXI\* MM, APB\*, AHB\*

- This is where ODSA can help!

## **Accelerating Innovation though Chiplets**

Advanced packaging is the technology enabler

Building out open source AIB IP to reduce chiplet design cost

"The ODSA aims to define an open interface such that chiplets from multiple vendors that support the interface can be assembled into domain-specific products." – Bapi Vinnakota

→ ODSA should tackle an ASIC-like module-tomodule protocol or protocols for chiplets